#### UNIVERSIDAD POLITÉCNICA SALESIANA

#### Sede Cuenca

Carrera Ingeniería Electrónica

#### TESIS DE PREGRADO

# "DISEÑO E IMPLEMENTACIÓN DEL SISTEMA DE CONTROL DE UN INVERSOR MULTINIVEL DE FUENTES INDEPENDIENTES, POR MEDIO DE MODULACIÓN VECTORIAL ESPACIAL"

por

Juan Carlos Galarza Galarza

Cuenca, diciembre 2012

#### UNIVERSIDAD POLITÉCNICA SALESIANA

#### SEDE CUENCA

#### CARRERA INGENIERÍA ELECTRÓNICA

Tesis previa a la obtención del título de Ingeniero Electrónico

#### "DISEÑO E IMPLEMENTACIÓN DEL SISTEMA DE CONTROL DE UN INVERSOR MULTINIVEL DE FUENTES INDEPENDIENTES, POR MEDIO DE MODULACIÓN VECTORIAL ESPACIAL"

**Autor:**

Juan Carlos Galarza Galarza

Director:

Ing. Flavio Quizhpi

Cuenca, diciembre 2012

Yo, Juan Carlos Galarza Galarza, con CI 0104167481, estudiante de la Universidad Politécnica Salesiana, me hago responsable de los conceptos desarrollados, análisis realizados y las conclusiones del presente trabajo. Autorizo a la Universidad Politécnica Salesiana el uso de este trabajo para fines académicos.

Cuenca, 30 de diciembre del 2012.

Juan Carlos Galarza Galarza CI: 0104167481

Luego de haber culminado el presente trabajo de tesis, certifico que el mismo fue realizado por el señor Juan Carlos Galarza Galarza.

Cuenca, 30 de diciembre del 2012.

Ing. Flavio Quizhpi

"No creo que haya alguna emoción más intensa para un inventor que ver alguna de sus creaciones funcionando. Esa emoción hace que uno se olvide de comer, de dormir, de todo" (Nikola Tesla).

#### **Dedicatoria**

Dedico esta tesis a mis padres, quienes con su incondicional apoyo y sus sabias enseñanzas, siempre me han guiado por el camino del bien.

A mis hermanos por su incondicional ayuda y sus palabras de aliento en las situaciones más dificiles.

#### **Agradecimientos**

Mi agradecimiento al profesor Flavio Quizhpi, quien confió en mí y mi trabajo y me brindo su apoyo humano y técnico, para la consecución de esta tesis.

A mi hermano Manolo quien siempre me apoyo y alentó en todo momento y sobre todo en los más duros, durante la consecución de esta tesis y a lo largo de mi vida.

También a Pablo Portocarrero, quien supo confiar en mí y prestarme la placa electrónica utilizada en esta tesis, también a la Universidad Politécnica Salesiana por facilitarme los laboratorios y equipos necesarios para la consecución de esta tesis.

# Índice general

| Int | trodu | ción    |                                                              | 1  |

|-----|-------|---------|--------------------------------------------------------------|----|

| 1.  | Mét   | odos d  | e modulación vectorial espacial.                             | 3  |

|     | 1.1.  | Métod   | os de modulación vectorial espacial.                         | 3  |

|     |       | 1.1.1.  | Introducción a los inversores multinivel                     | 3  |

|     |       | 1.1.2.  | Clasificación de los inversores multinivel                   | 4  |

|     |       | 1.1.3.  | Topologías para inversores multinivel de fuentes de tensión. | 5  |

|     |       | 1.1.4.  | Métodos de modulación para inversores multinivel             | 10 |

|     |       | 1.1.5.  | Métodos de modulación vectorial espacial                     | 13 |

|     | 1.2.  | Ventaj  | as y desventajas de los métodos de modulación vectorial      |    |

|     |       | espacia | al                                                           | 14 |

| 2.  | Dise  | eño del | sistema de control.                                          | 16 |

|     | 2.1.  | Modul   | ación vectorial espacial elegido                             | 16 |

|     |       | 2.1.1.  | Introducción                                                 | 16 |

|     |       | 2.1.2.  | Transformada de Park                                         | 17 |

|     |       | 2.1.3.  | Método de modulación vectorial de consideraciones geomé-     |    |

|     |       |         | tricas                                                       | 20 |

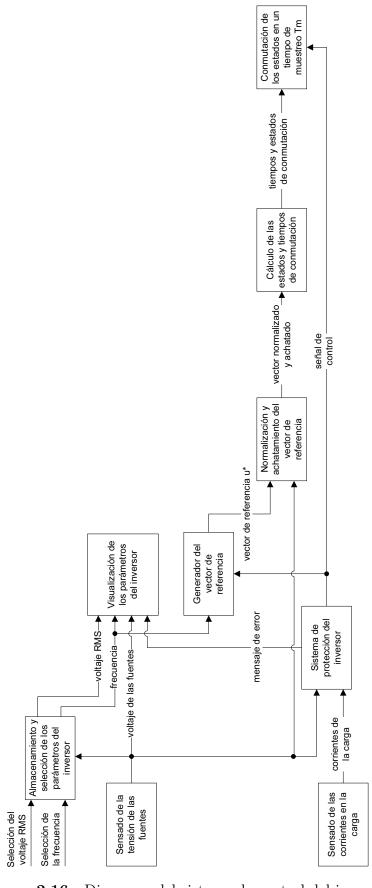

|     | 2.2.  | Descri  | pción del sistema de control.                                | 50 |

|     |       | 2.2.1.  | Descripción                                                  | 53 |

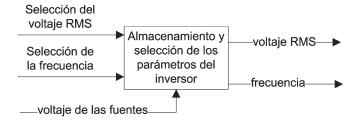

|     |       | 2.2.2.  | Almacenamiento y selección de los parámetros del inversor.   | 54 |

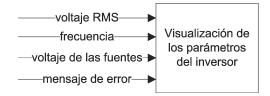

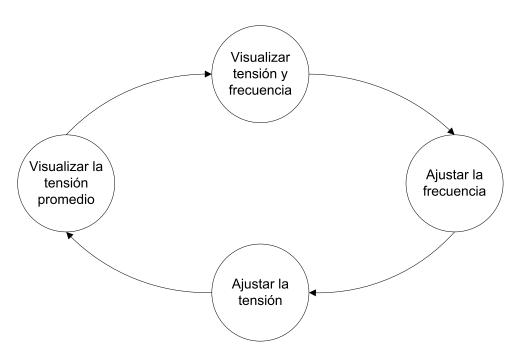

|     |       | 2.2.3.  | Visualización de los parámetros del inversor                 | 55 |

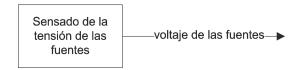

|     |       | 2.2.4.  | Sensado de la tensión de las fuentes                         | 55 |

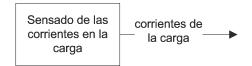

|     |       | 2.2.5.  | Sensado de las corrientes en la carga                        | 56 |

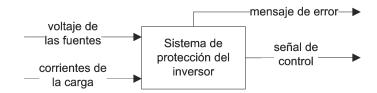

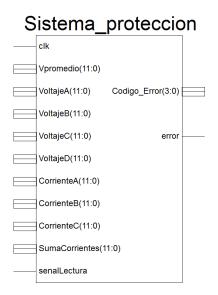

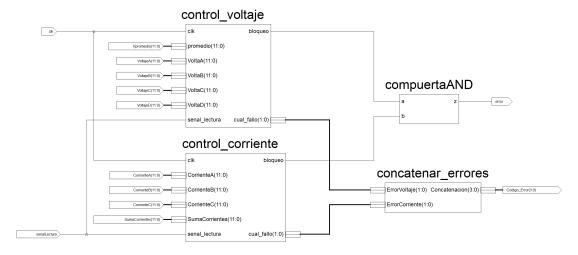

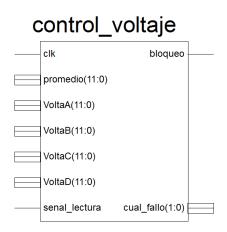

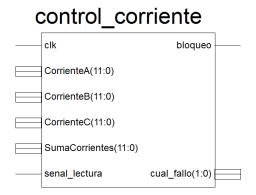

|     |       | 2.2.6.  | Sistema de protección del inversor                           | 56 |

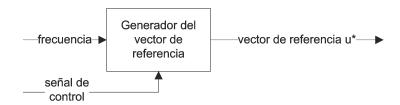

|     |       | 2.2.7.  | Generador del vector de referencia                           | 57 |

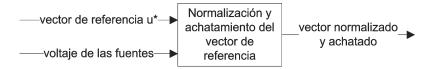

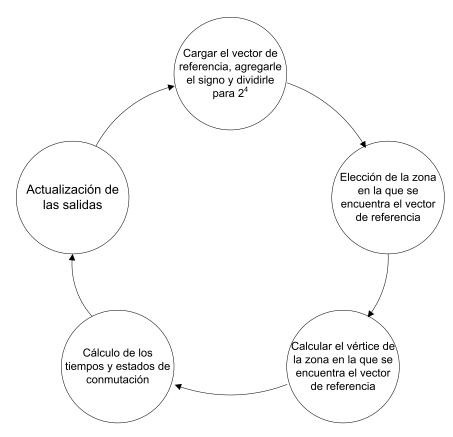

|     |       | 2.2.8.  | Normalización y achatamiento del vector de referencia        | 57 |

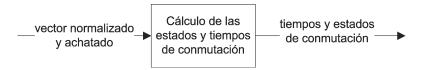

|     |       | 2.2.9.  | Cálculo de los estados y tiempos de conmutación              | 58 |

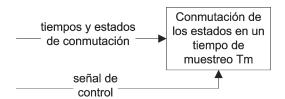

|     |       | 2.2.10. | Conmutación de los estados en un tiempo de muestreo $T_m$ .  | 58 |

| 3. | Dise | eño de                                         | la parte eléctrica y electrónica.                          | 60  |  |

|----|------|------------------------------------------------|------------------------------------------------------------|-----|--|

|    | 3.1. | . Tipos de topologías de inversores multinivel |                                                            |     |  |

|    | 3.2. | Topolo                                         | ogía de fuentes independientes                             | 61  |  |

|    | 3.3. | Diseño                                         | o de la topología multinivel utilizada                     | 61  |  |

|    |      | 3.3.1.                                         | Descripción básica de los IGBT's                           | 62  |  |

|    |      | 3.3.2.                                         | Descripción de la topología usada                          | 63  |  |

|    |      | 3.3.3.                                         | Estados del convertidor de fuentes independientes de 4 ni- |     |  |

|    |      |                                                | veles                                                      | 69  |  |

|    |      | 3.3.4.                                         | Máxima tensión que puede generar el inversor               | 73  |  |

| 4. | Prog | gramac                                         | ción del algoritmo de control.                             | 76  |  |

|    | 4.1. | Sistem                                         | na FPGA                                                    | 76  |  |

|    |      | 4.1.1.                                         |                                                            | 76  |  |

|    |      | 4.1.2.                                         | Tipos de FPGA's                                            | 77  |  |

|    |      | 4.1.3.                                         | Ventajas y desventajas de los FPGA's                       | 78  |  |

|    |      | 4.1.4.                                         | Lenguajes de programación para FPGA                        | 79  |  |

|    | 4.2. | Simula                                         | ación del algoritmo de control                             | 80  |  |

|    |      | 4.2.1.                                         | Simulación del algoritmo de consideraciones geométrica en  |     |  |

|    |      |                                                | Matlab                                                     | 80  |  |

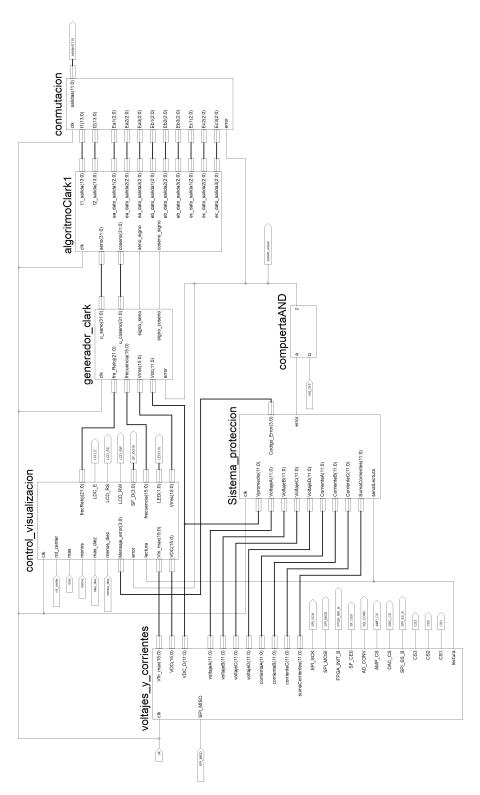

|    | 4.3. | Diagra                                         | ama de bloques del algoritmo de control                    | 86  |  |

|    |      | 4.3.1.                                         | MicroBlaze Development Kit Spartan-3E 1600E                | 88  |  |

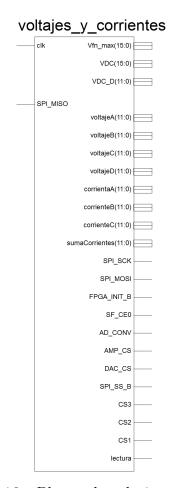

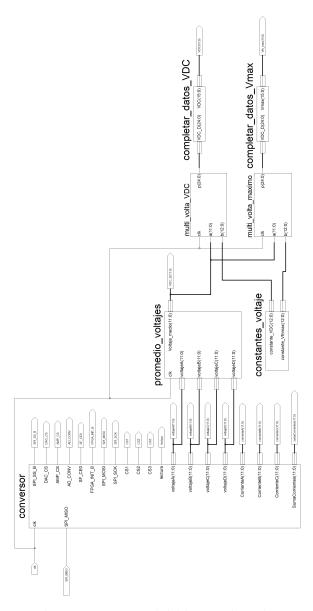

|    |      | 4.3.2.                                         | Voltajes y corrientes                                      | 89  |  |

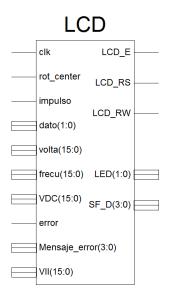

|    |      | 4.3.3.                                         | Control y visualización                                    | 111 |  |

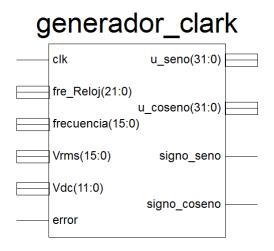

|    |      | 4.3.4.                                         | Generador de Clark                                         | 119 |  |

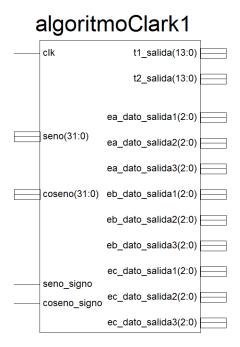

|    |      | 4.3.5.                                         | Algoritmo Clark 1                                          | 132 |  |

|    |      | 4.3.6.                                         | Conmutación                                                | 134 |  |

|    |      | 4.3.7.                                         | Sistema de protección                                      | 139 |  |

| 5. | Pru  | ebas de                                        | e funcionamiento.                                          | 145 |  |

|    | 5.1. | Simula                                         | ación del algoritmo mediante Isim.                         | 145 |  |

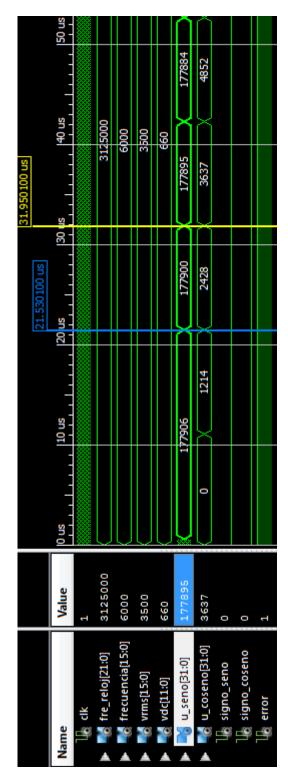

|    |      | 5.1.1.                                         | Simulación del bloque del generador de Clark               | 145 |  |

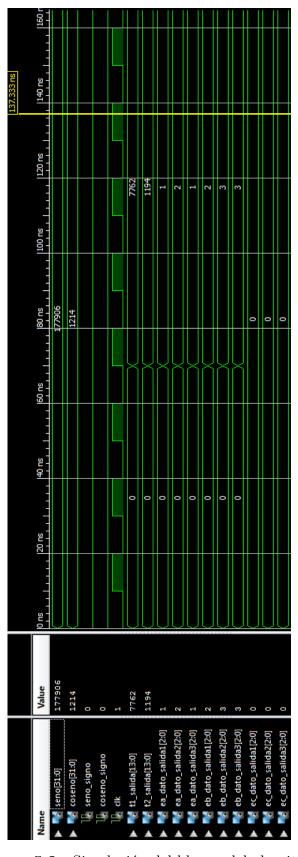

|    |      | 5.1.2.                                         | Simulación del bloque del algoritmo                        | 148 |  |

|    | 5.2. | Verific                                        | eación del algoritmo mediante ChipScope                    | 152 |  |

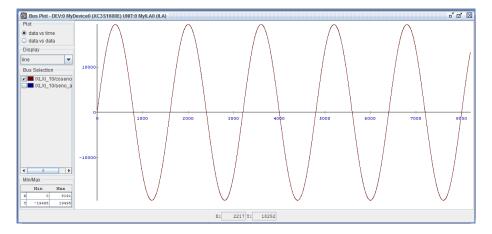

|    |      | 5.2.1.                                         | Verificación del bloque del generador de Clark             | 152 |  |

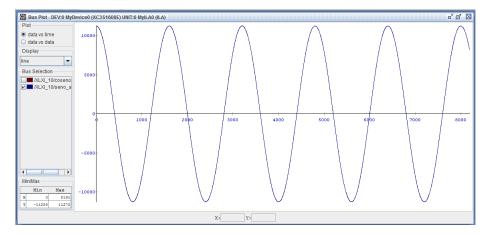

|    |      | 5.2.2.                                         | Verificación del bloque del algoritmo                      | 154 |  |

|    | 5.3. | Prueb                                          | as del algoritmo con el circuito de potencia               | 157 |  |

|    |      | 5.3.1.                                         | Prueba con carga resistiva                                 | 157 |  |

#### Índice general

| 5.3.2.         | Pruebas con carga resistiva inductiva en serie | 159 |

|----------------|------------------------------------------------|-----|

| 5.3.3.         | Pruebas con un motor asíncrono de 4 polos      | 160 |

| 6. Analisis de | resultados.                                    | 169 |

| Concluciones   |                                                | 172 |

| Recomendacio   | nes                                            | 175 |

| A. Estados del | l inversor de 4 niveles.                       | 176 |

| B. Algoritmo d | de consideraciones geométricas en Matlab.      | 193 |

| Bibliografía   |                                                | 200 |

| Nomenclatura   |                                                | 202 |

# Índice de figuras

| 1.1.  | Elementos de un Inversor Multinivel                                 | 3  |

|-------|---------------------------------------------------------------------|----|

| 1.2.  | Ondas de un inversor multinivel                                     | 4  |

| 1.3.  | Inversor de medio puente y circuito equivalente                     | 5  |

| 1.4.  | Inversor de tres niveles NPC                                        | 6  |

| 1.5.  | Conversor NPC de 3 niveles y de n niveles                           | 7  |

| 1.6.  | Esquema de un inversor de tres niveles DMC                          | 8  |

| 1.7.  | Mallas de condensadores del inversor DMC                            | 8  |

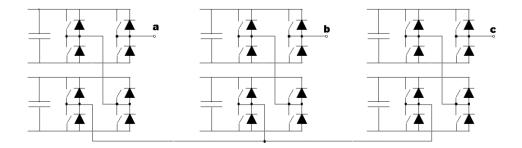

| 1.8.  | Inversores monofásico en cascada                                    | 9  |

| 1.9.  | Inversor trífasico en cascada                                       | 9  |

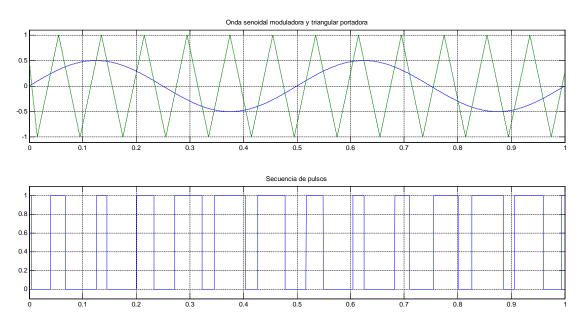

| 1.10. | Onda senoidal moduladora y triangular portadora                     | 11 |

| 1.11. | Ondas senoidal moduladora y triangulares portadoras para inver-     |    |

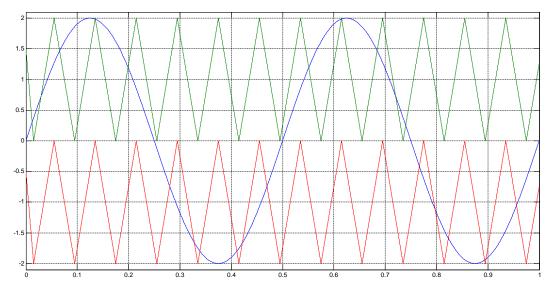

|       | sores multinivel                                                    | 12 |

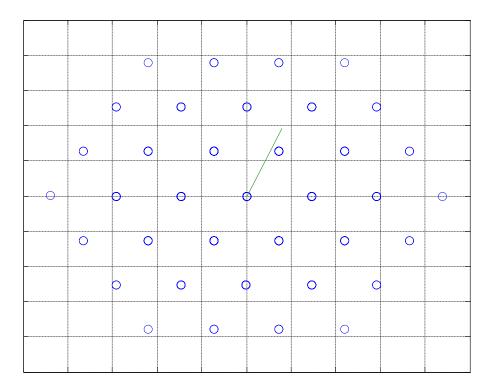

| 1.12. | Espacio vectorial de un inversor de 4 niveles                       | 13 |

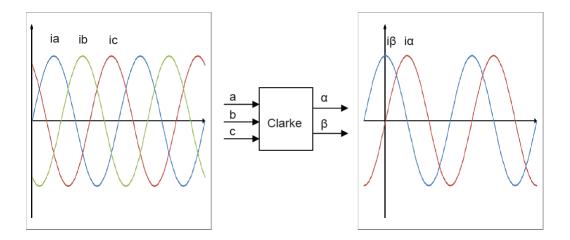

| 2.1.  | Transformada de Clark [1]                                           | 18 |

| 2.2.  | Transformada de Park [1]                                            | 19 |

| 2.3.  | Hexágonos normales y normalizados                                   | 21 |

| 2.4.  | Espacio de estados normalizados                                     | 22 |

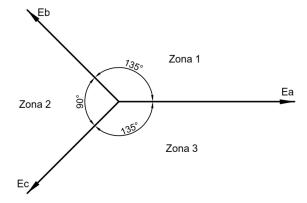

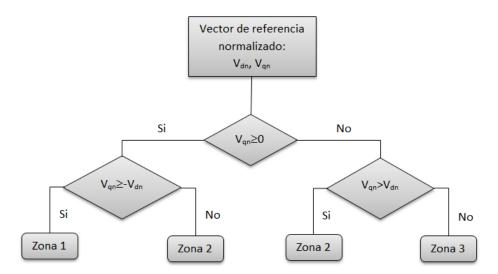

| 2.5.  | Zonas del plano achatado                                            | 22 |

| 2.6.  | Flujograma para determinar la zona en la que se encuentra el vector |    |

|       | de referencia                                                       | 23 |

| 2.7.  | Vectores de estado de un convertidor de 5 niveles de la zona 1      | 24 |

| 2.8.  | Vectores de estado de un convertidor de 5 niveles de la zona 2      | 25 |

| 2.9.  | Vectores de estado de un convertidor de 5 niveles de la zona 3      | 27 |

| 2.10. | Región geométrica en la zona 1                                      | 29 |

| 2.11. | Región geométrica en la zona 2                                      | 31 |

| 2.12. | Región geométrica en la zona 3                                      | 33 |

| 2.13. | Coordenadas de los niveles del inversor de la zona 1                | 34 |

| 2.14. | Coordenadas de los niveles del inversor de la zona 2                | 35 |

| 2.15. | Coordenadas de los niveles del inversor de la zona 3                       | 35 |

|-------|----------------------------------------------------------------------------|----|

| 2.16. | Diagrama del sistema de control del inversor                               | 52 |

| 2.17. | Bloque de almacenamiento y selección de los parámetros del inversor.       | 54 |

| 2.18. | Bloque de visualización de los parámetros del inversor                     | 55 |

| 2.19. | Bloque de sensado de la tensión de las fuentes                             | 55 |

| 2.20. | Bloque de sensado de la corriente en la carga                              | 56 |

| 2.21. | Bloque del sistema de protección del inversor                              | 56 |

| 2.22. | Bloque del generador del vector de referencia                              | 57 |

| 2.23. | Bloque de normalización y achatamiento del vector de referencia.           | 58 |

| 2.24. | Bloque de cálculo de los estados y tiempos de conmutación                  | 58 |

| 2.25. | Bloque de conmutación de los estados en un tiempo de muestreo ${\cal T}_m$ | 59 |

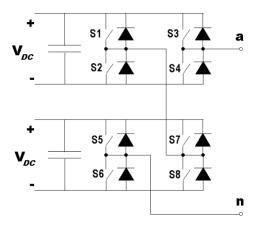

| 3.1.  | Rama de un convertidor de puentes monofásicos de 5 niveles                 | 61 |

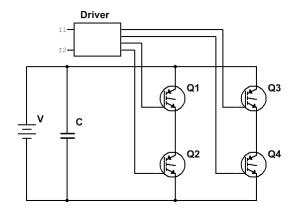

| 3.2.  | Convertidor trifásico de puentes monofásicos en estrella de 3 niveles.     | 62 |

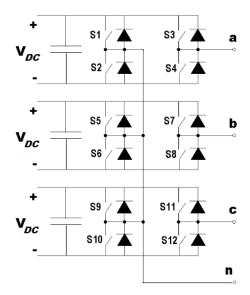

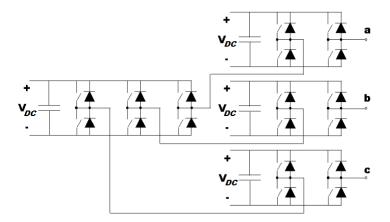

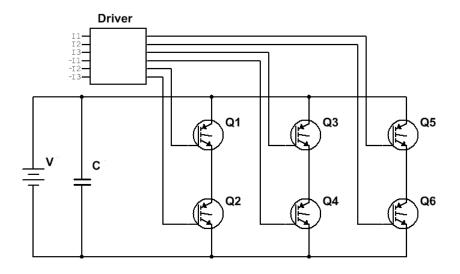

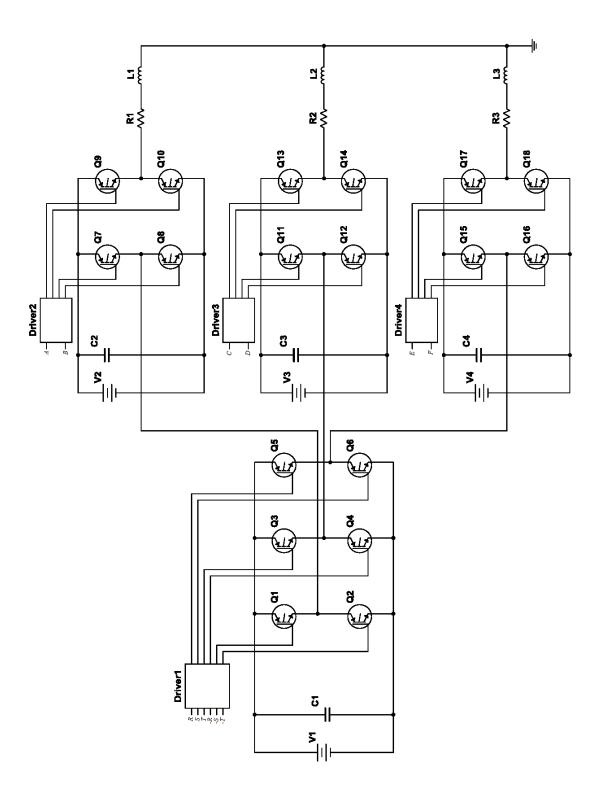

| 3.3.  | Convertidor trífasico de puentes en cascada de 4 niveles                   | 62 |

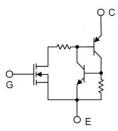

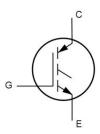

| 3.4.  | Circuito equivalente del IGBT                                              | 63 |

| 3.5.  | Símbolo del IGBT                                                           | 63 |

| 3.6.  | Fuente DC PE-5000 de K and H                                               | 64 |

| 3.7.  | Esquema del convertidor monofásico                                         | 65 |

| 3.8.  | Banco de IGBT's monofásico PE-5310-4F de K and H                           | 65 |

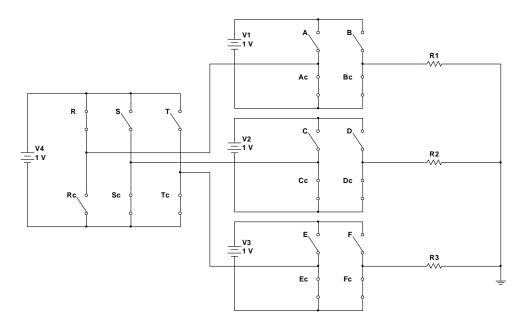

| 3.9.  | Esquema del puente convertidor trifásico                                   | 66 |

| 3.10. | Banco de IGBT's universales PE-5310-4F de K and H                          | 66 |

| 3.11. | Transductor de corriente PE-5310-2C de K and H                             | 67 |

| 3.12. | Esquema del conversor de fuentes independientes de $4$ niveles. $$ .       | 68 |

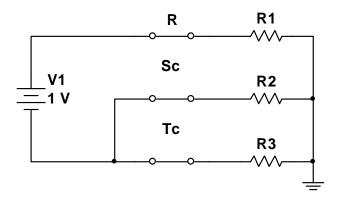

| 3.13. | Estado 100000000 del convertidor de 4 niveles                              | 69 |

| 3.14. | Estado simplificado $1000000000$ del convertidor de 4 niveles              | 70 |

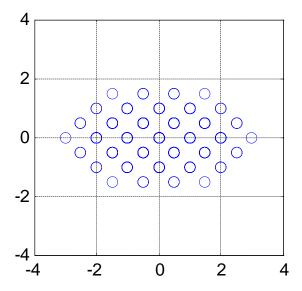

| 3.15. | Espacio vectorial normalizado del inversor de 4 niveles                    | 71 |

| 3.16. | Espacio vectorial en donde el inversor no se satura                        | 75 |

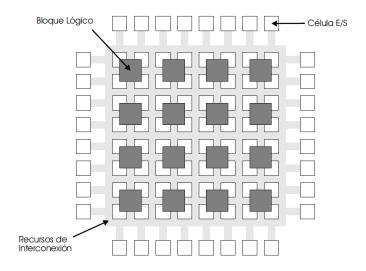

| 4.1.  | Estructura general de un FPGA[2]                                           | 77 |

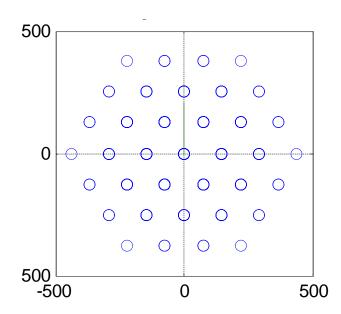

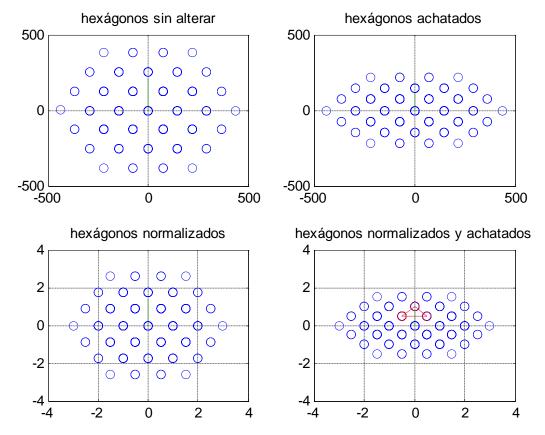

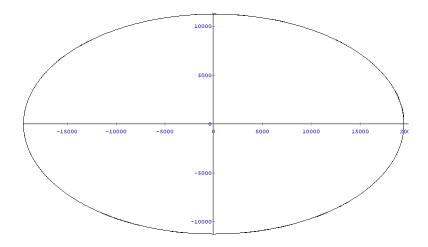

| 4.2.  | Espacio vectorial y vector de referencia sin alterar                       | 81 |

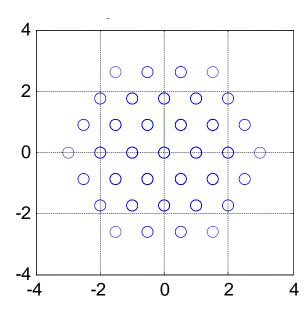

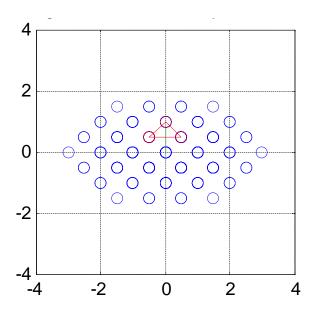

| 4.3.  | Espacio vectorial y vector de referencia normalizado                       | 83 |

| 4.4.  | Espacio vectorial y vector de referencia normalizado y achatado            | 84 |

| 4.5.  | Espacios vectoriales en las distintas etapas del algoritmo                 | 85 |

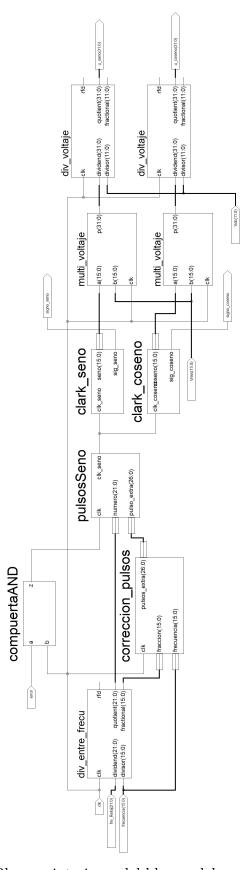

| 4.6.  | Diagrama de bloques montado en el sistema FPGA                             | 87 |

| 4.7.  | Tarjeta Micro<br>Blaze Development Kit Spartan-3<br>E 1600<br>E[3]         | 89 |

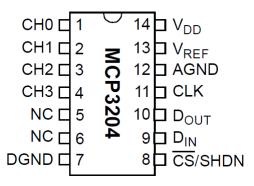

| 4.8.  | Distribución de pines del MCP3204[4]                                       | 90 |

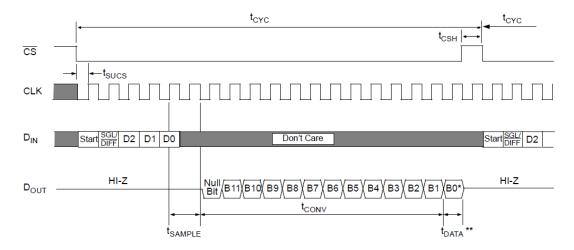

| 4.9.  | Comunicación con el MCP3204[4]                                         |

|-------|------------------------------------------------------------------------|

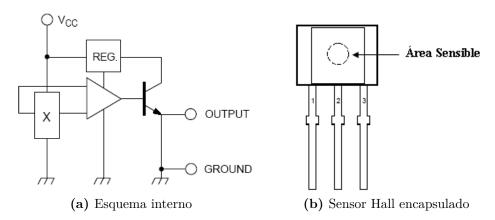

| 4.10. | Sensor de efecto Hall[5]                                               |

| 4.11. | Circuito de resistencias del voltaje de referencia para la medición    |

|       | de tensión de las fuentes                                              |

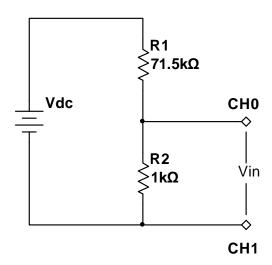

| 4.12. | Partidor de tensión para la medición de la tensión de las fuentes 94   |

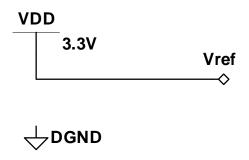

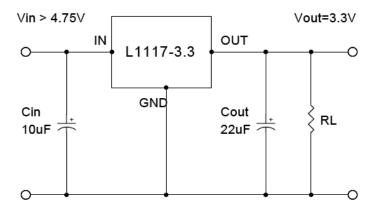

| 4.13. | Fuente de 3.3v                                                         |

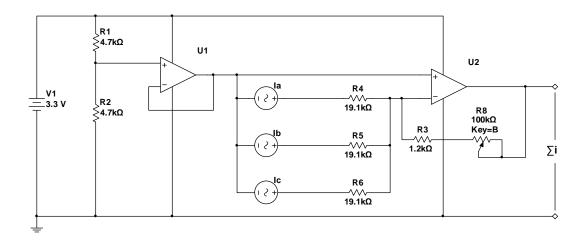

| 4.14. | Circuito de acoplamiento para la medición de la suma de corrientes. 96 |

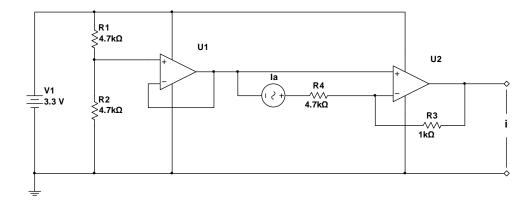

| 4.15. | Circuito acoplador para la medición de la corriente en la carga 98     |

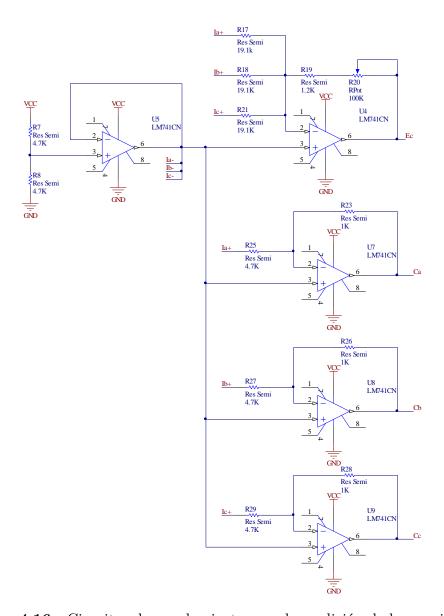

| 4.16. | Circuitos de acoplamiento para la medición de las corrientes 99        |

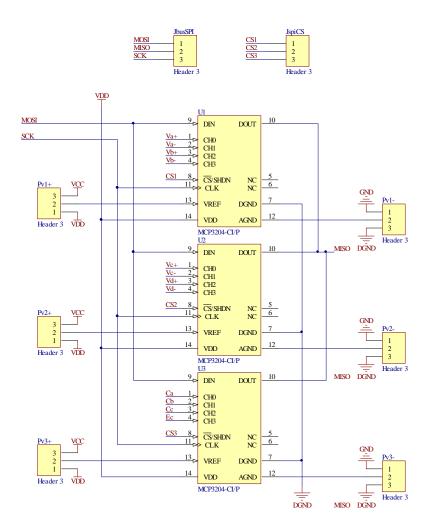

| 4.17. | Conexión de los MCP3204                                                |

| 4.18. | Bloque de voltajes y corrientes                                        |

| 4.19. | Bloques internos del bloque de voltajes y corrientes                   |

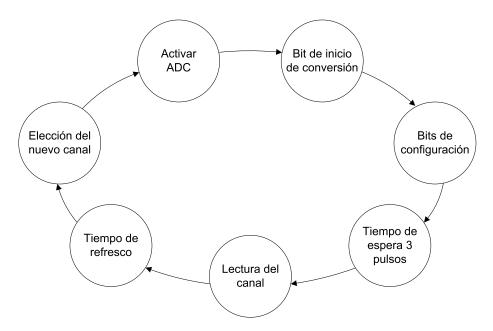

| 4.20. | Bloque de control del conversor analógico digital 104                  |

| 4.21. | Maquina de estados para el control de los ADC's 106                    |

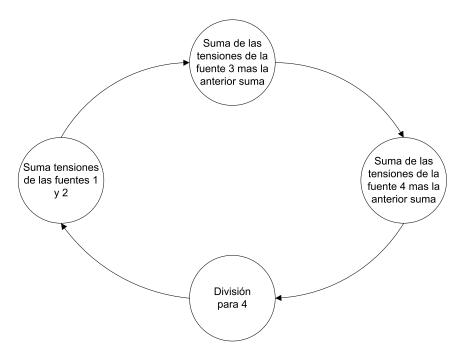

| 4.22. | Bloque para el promediado de las tensiones de la fuente 107            |

| 4.23. | Maquina de estados del bloque del promediado de tensiones $107$        |

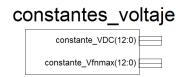

| 4.24. | Bloque de constantes de voltaje                                        |

| 4.25. | Bloques de multiplicación del voltaje VDC                              |

| 4.26. | Bloques para completar datos de voltaje                                |

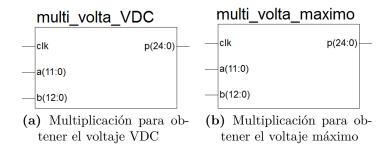

| 4.27. | Bloque de control y visualización                                      |

| 4.28. | Bloques interiores del bloque de control y visualización               |

| 4.29. | Bloque de manejo del scroll                                            |

| 4.30. | Maquina de estados del botón de selección                              |

| 4.31. | Bloque de cálculo del voltaje de linea                                 |

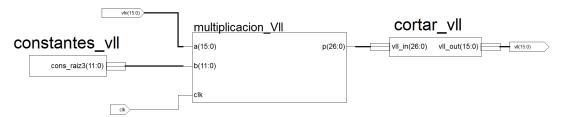

| 4.32. | Bloques interiores del bloque voltaje vll                              |

| 4.33. | Bloque de manejo del LCD                                               |

| 4.34. | Bloque del generador de Clark                                          |

| 4.35. | Bloques interiores del bloque del generador de Clark                   |

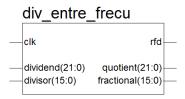

| 4.36. | Bloque de división entre frecuencias                                   |

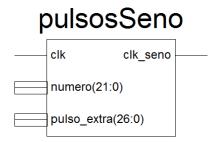

| 4.37. | Bloque del generador de pulsos                                         |

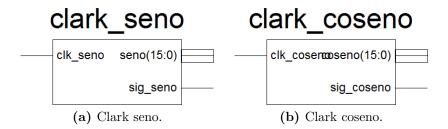

| 4.38. | Bloques de generación de las componentes d y q del vector de           |

|       | referencia                                                             |

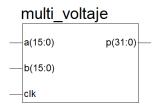

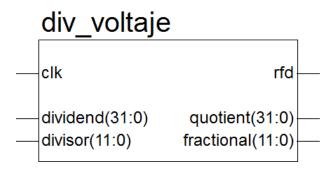

| 4.39. | Multiplicación de voltajes                                             |

| 4.40. | División de voltaje                                                    |

| 4.41. | Bloque del algoritmo Clark                                             |

| 4.42. | Maquina de estados del algoritmo                                       |

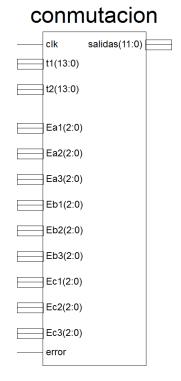

| 1 12  | Rloque de conmutación                                                  |

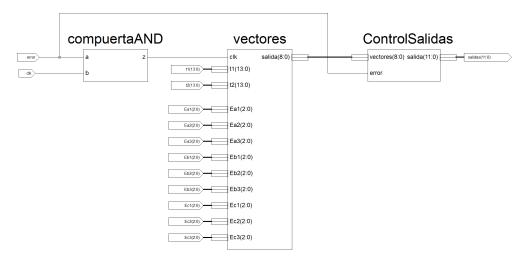

| 4.44. Bloques interiores del bloque de conmutación                                        |

|-------------------------------------------------------------------------------------------|

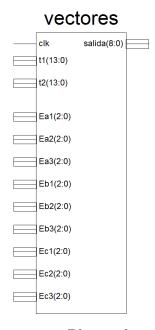

| 4.45. Bloque de vectores                                                                  |

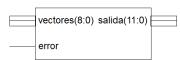

| 4.46. Bloque de control de salidas                                                        |

| 4.47. Bloque del sistema de protección                                                    |

| 4.48. Bloques interiores del sistema de protección                                        |

| 4.49. Bloque de control de voltajes                                                       |

| 4.50. Bloque de control de corrientes                                                     |

| 5.1. Simulación del bloque del generador de Clark                                         |

| 5.2. Simulación del bloque del algoritmo                                                  |

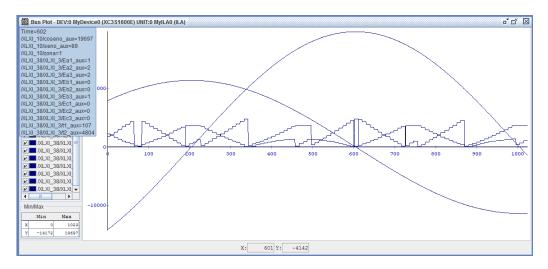

| 5.3. Componente d del vector de referencia capturado por el ChipScope. 153                |

| 5.4. Componente q del vector de referencia capturado por el ChipScope. 153                |

| 5.5. Espacio vectorial capturado con el ChipScope                                         |

| 5.6. Estados y tiempos de conmutación capturados por medio del ChipS-                     |

| cope                                                                                      |

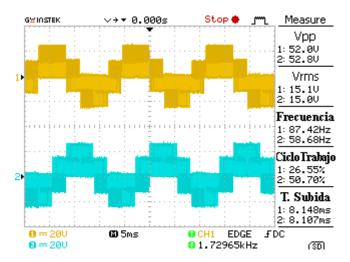

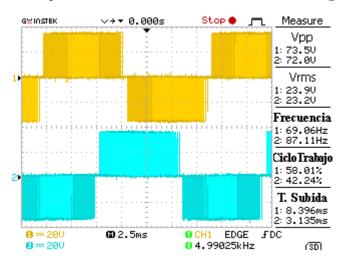

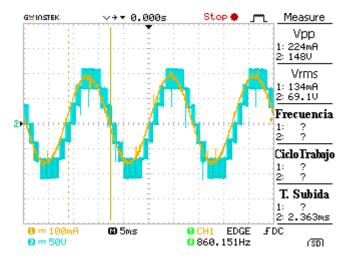

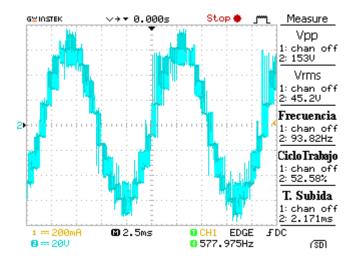

| 5.7. Tensiones fase neutro medidas en 2 de las fases                                      |

| 5.8. Frecuencia de salida con una carga de 300 $\Omega$                                   |

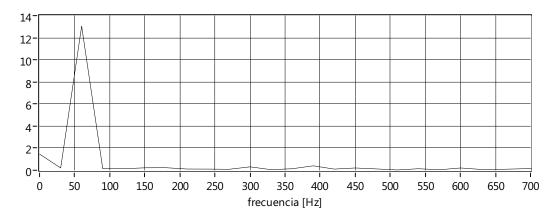

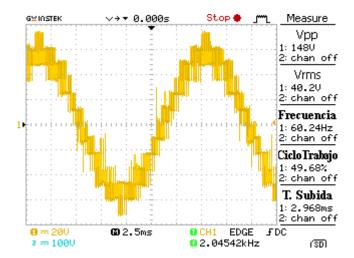

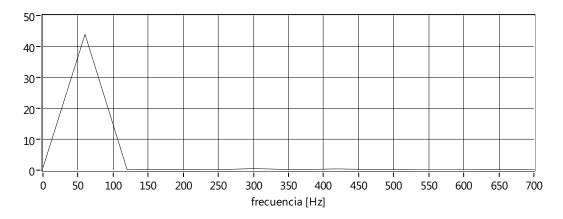

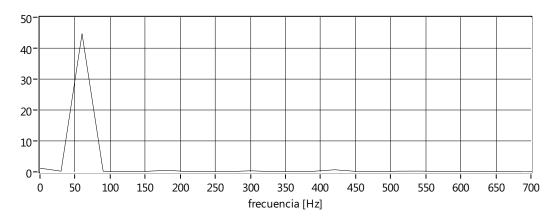

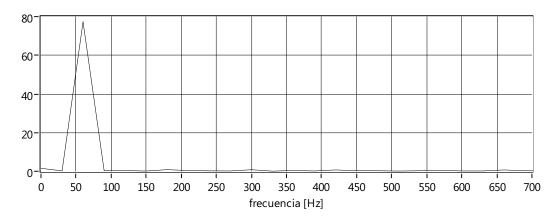

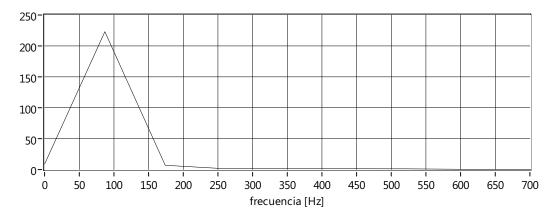

| 5.9. Espectro de la onda de tensión con una carga de 300 $\Omega$ 159                     |

| 5.10. Tensión linea linea en 2 de las fases con una carga R 159                           |

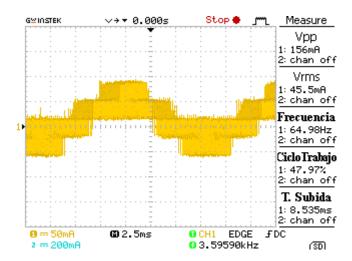

| 5.11. Corriente en una de las fases con una carga R                                       |

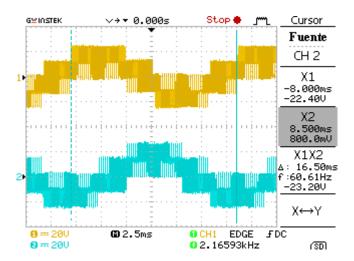

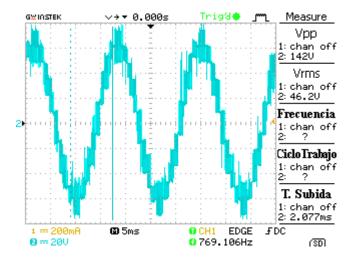

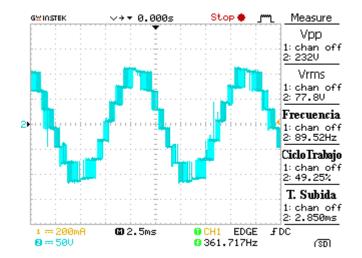

| 5.12. Tensión fase neutro en 2 de las fases con carga RL 160                              |

| 5.13. Frecuencia y tensión fase neutro en la onda de tensión de salida                    |

| con carga RL                                                                              |

| 5.14. Espectro de la onda de tensión con una carga RL                                     |

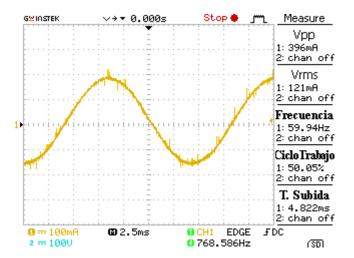

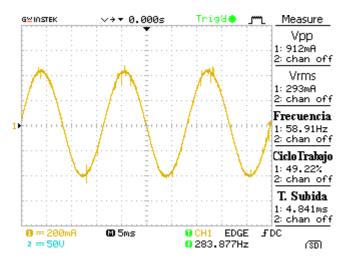

| 5.15. Corriente de fase con una carga RL                                                  |

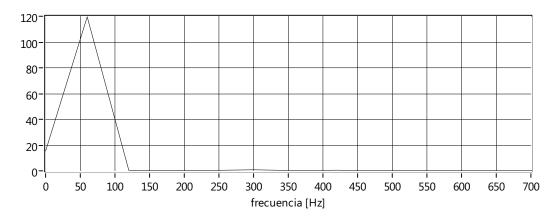

| 5.16. Espectro de la onda de corriente con una carga RL 162                               |

| 5.17. Tensión de fase y corriente de fase con carga RL                                    |

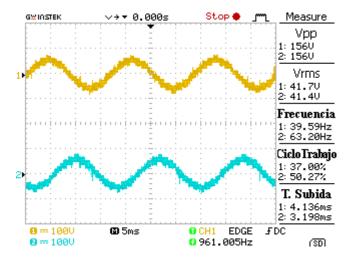

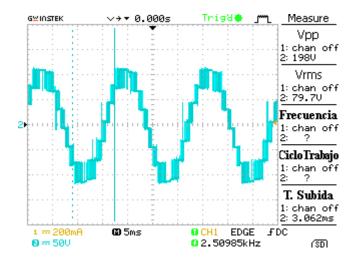

| 5.18. Tensión fase neutro del motor a 60Hz                                                |

| 5.19. Tensión linea linea del motor a 60Hz                                                |

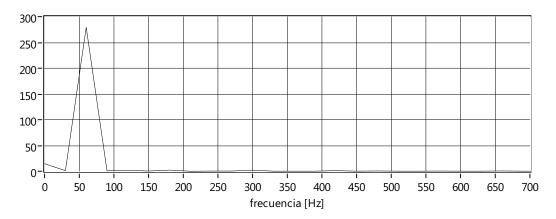

| $5.20.$ Espectro de la onda de tensión de fase, con el motor a $60\mathrm{Hz}.~\dots~164$ |

| $5.21.$ Espectro de la onda de tensión de linea, con el motor a $60\mathrm{Hz}.$ $$ $$ $$ |

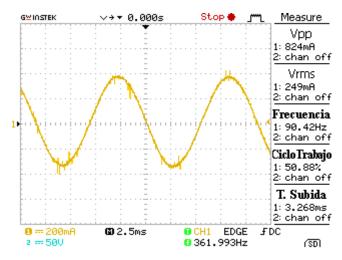

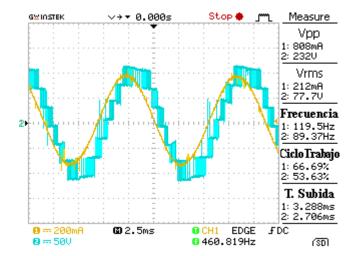

| 5.22. Corriente del motor a 60Hz                                                          |

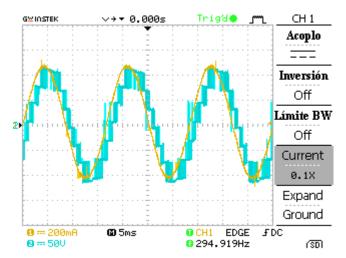

| 5.23. Espectro de la onda de corriente, con el motor a 90Hz 166                           |

| 5.24. Tensión de fase y corriente del motor a 60Hz 166                                    |

| 5.25. Tensión fase neutro del motor a 90Hz                                                |

| 5.26. Tensión linea linea del motor a 90Hz                                                |

| 5.27. Corriente del motor a 90Hz                                                          |

#### Índice de figuras

| 5.28. | Espectro de la onda de corriente, con el motor a 90Hz | 168 |

|-------|-------------------------------------------------------|-----|

| 5.29. | Tensión de fase y corriente del motor a 90Hz          | 168 |

### Índice de tablas

| 1.1. | Comparación entre los requerimientos de componentes de las to-<br>pologías básicas | 9   |

|------|------------------------------------------------------------------------------------|-----|

| 2.1. | Vectores de estado y tiempos de conmutación en las 3 zonas del plano complejo      | 51  |

| 3.1. | Estados del convertidor monofásico                                                 | 64  |

| 3.2. | Estados del convertidor trifásico                                                  | 66  |

| 3.3. | Estados utilizados en este trabajo transformado al plano d-q                       | 72  |

| 4.1. | Descripción de los pines del MCP3204[4]                                            | 90  |

| 4.2. | Bits de configuración del MCP3204[4]                                               | 91  |

| 4.3. | Valores para la desactivación de los demás periféricos en el bus                   |     |

|      | SPI[3]                                                                             | 106 |

| A.1. | Estados del inversor de 4 niveles de fuentes independientes del 0                  |     |

|      | al 31                                                                              | 177 |

| A.2. | Estados del inversor de 4 niveles de fuentes independientes del 32                 |     |

|      | al 63                                                                              | 178 |

| A.3. | Estados del inversor de 4 niveles de fuentes independientes del 64                 |     |

|      | al 95                                                                              | 179 |

| A.4. | Estados del inversor de 4 niveles de fuentes independientes del 96                 |     |

|      | al 127                                                                             | 180 |

| A.5. | Estados del inversor de 4 niveles de fuentes independientes del 128                |     |

|      | al 159                                                                             | 181 |

| A.6. | Estados del inversor de 4 niveles de fuentes independientes del 160                |     |

|      | al 191                                                                             | 182 |

| A.7. | Estados del inversor de 4 niveles de fuentes independientes del 192                |     |

|      | al 223                                                                             | 183 |

| A.8. | Estados del inversor de 4 niveles de fuentes independientes del 224                |     |

|      | al 255                                                                             | 184 |

| A.9. Estados del inversor de 4 niveles de fuentes independientes del 256     |     |

|------------------------------------------------------------------------------|-----|

| al 287                                                                       | 185 |

| A.10. Estados del inversor de 4 niveles de fuentes independientes del 288    |     |

| al 319                                                                       | 186 |

| A.11. Estados del inversor de 4 niveles de fuentes independientes del 320 $$ |     |

| al 351                                                                       | 187 |

| A.12. Estados del inversor de 4 niveles de fuentes independientes del 352    |     |

| al 383                                                                       | 188 |

| A.13. Estados del inversor de 4 niveles de fuentes independientes del 384    |     |

| al 415                                                                       | 189 |

| A.14. Estados del inversor de 4 niveles de fuentes independientes del 416    |     |

| al 447                                                                       | 190 |

| A.15.Estados del inversor de 4 niveles de fuentes independientes del 448     |     |

| al 479                                                                       | 191 |

| A.16.Estados del inversor de 4 niveles de fuentes independientes del 480     |     |

| al 511                                                                       | 192 |

#### Introducción

Desde la introducción de los convertidores CD/CA ya hace varios años, su estudio y utilización se han venido incrementado, debido a sus diversas aplicaciones, que van desde variadores de frecuencia para motores asíncronos hasta para sistema de corrección del factor de potencia y/o para la compensación de corrientes reactivas.

Estos conversores CD/CA también llamados inversores, tienen la función de convertir una tensión fija de corriente continua a una tensión simétrica de corriente alterna con frecuencia y tensión deseada, esta frecuencia y tensión pueden ser ajustables según se desee en ciertos casos.

La tensión simétrica alterna se consigue al conectar la carga a la fuente de alimentación en un sentido u otro, por medio de interruptores de potencia, los mismo que pueden conmutar varias veces por ciclos para conseguir la tensión deseada.

Estos interruptores de potencia también han permitido el adelanto en cuanto a los inversores, ya que los mismo se han vuelto más rápidos y con una mayor potencia con el paso de los años, lo que ha generado una serie de técnicas de control, que van desde las basadas en la generación de ondas cuadradas simétricas a la frecuencia deseada, los que necesitan semiconductores de baja velocidad, pasado por técnicas PWM con requerimiento de semiconductores de gran velocidad, pero con la ventaja se consigue una menor distorsión armónica y un ajuste de la tensión de salida casi independiente de la fuente de tensión de la alimentación, hasta técnicas más avanzadas, como el control vectorial espacial, que al igual que las técnicas PWM necesitan semiconductores de gran velocidad, pero con prestaciones aun mejores que la técnica PWM, ya que la distorsión armónica es mucho menor y también un control más exacto de la tensión a obtener a la salida.

También estas tensiones a obtener en la salida, han desencadenado una serie de estudios de la estructura de los inversores llamadas topologías, las cuales van desde la más simple con 3 niveles en donde se hace conmutar los interruptores para que a la carga le llegue una tensión igual a 0 voltios, más o menos la tensión de alimentación, hasta las topologías multinivel en donde la tensión que le llega a

la carga es una fracción de la tensión de alimentación o se conectan varias fuentes en cascada para generar los distintos niveles a su salida.

Las topologías multinivel ofrecen varias ventajas con respecto a las topologías de 3 niveles, ya que salida produce una menor distorsión armónica y también que necesitan semiconductores de potencia de menores voltajes porque solo manejan una fracción de la tensión de alimentación, que en los casos de inversores de potencia pueden ser una gran ventaja porque a mayor tensión que maneja un semiconductor, su costo es muchísimo mayor.

Una de las topologías que se usan generalmente, es la topología de fuentes independientes también conocida como de puentes monofásicos en cascada, tiene la característica de que puede implementarse de forma modular, ya que para incrementar los niveles solo basta con agregar más puentes en cascada, ademas esta topología es controlada por medio de técnicas de control vectorial espacial por su eficiencia, y principalmente por que en la actualidad los dispositivos electrónicos como los DSP y FPGA, utilizados para su control se han abarato.

El abaratamiento de los FPGA y DSP, han permitido estudiar de una manera más detallada del comportamiento de esta topología de fuentes independientes, como la realizada en este trabajo, en donde se investigo algunos de estos algoritmos de vector espacial y se puso a prueba el funcionamiento de uno de estos, el de consideraciones geométricas descrito en [6] y se probo su funcionamiento, el algoritmo se implemento en un sistema FPGA, y se probo sobre un motor asíncrono, verificando su comportamiento.

# 1. Métodos de modulación vectorial espacial.

#### 1.1. Métodos de modulación vectorial espacial.

#### 1.1.1. Introducción a los inversores multinivel.

Los inversores multinivel y los inversores convencionales, son sistemas electrónicos destinados principalmente a transformar de corriente continua a corriente alterna y su utilización esta en aumento, debido principalmente a sus posibles aplicaciones en el futuro, en sistemas de energía renovable[7] en corrección de factores de potencia o eliminación de armónicos en las redes de transmisión y distribución eléctricas [8].

Los inversores multinivel como ya se menciono convierten de corriente continua a corriente alterna, tienen la característica que utilizan más un nivel de voltaje para generar la onda seno a su salida, desencadenando una serie de ventajas con respecto a los convertidores convencionales de un solo nivel, como son menores contenidos armónicos entre otros, que son de especial interés en sistemas eléctricos de potencia ya que son usados para inyectar energía en las mismas a partir de fuentes de continua[6].

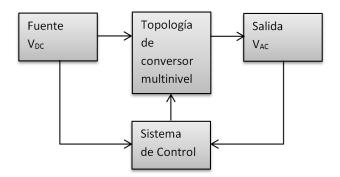

Figura 1.1.: Elementos de un Inversor Multinivel.

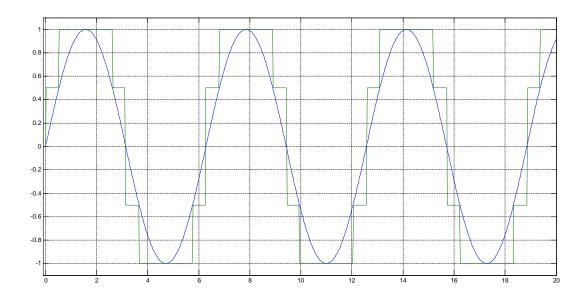

Los inversores multinivel como se ve en la Figura 1.1, son sistemas de semiconductores electrónicos de potencia, fuentes de voltaje, condensadores y sistemas de control, arreglados de tal forma que a partir de fuentes de corriente continua o condensadores conectadas a los semiconductores electrónicos de potencia (Topología de conversor multinivel) se cierran y abren , por el mando del sistema de control, para generan ondas cuadradas moduladas o no, que tratan de asemejarse a una onda senoidal a su salida como se ve en la Figura 1.2, ademas el sistema de control recibe señales de las fuentes de tensión y de la salida para mejorar su eficiencia.

Figura 1.2.: Ondas de un inversor multinivel

#### 1.1.2. Clasificación de los inversores multinivel

Los inversores multinivel según [6], pueden clasificarse de varias formas pero entre las principales son las siguientes:

- Tipo de fuentes de continua.

- Fuente de corriente

- Fuente de tensión

- Tipo de dispositivos interruptores.

- BJT

- MOSFET

- Tiristor

- GTO

- IGBT

- IGCT

- Tipo de topología usado.

- Convertidores de niveles

- Convertidores multinivel

- Técnica de control usado.

- Baja frecuencia: onda cuadrada como la mostrada en la Figura 1.2.

- Alta frecuencia: con modulación por ancho de pulso o vectorial espacial

## 1.1.3. Topologías para inversores multinivel de fuentes de tensión.

La topología de un conversor o inversor multinivel, es la disposición de los semiconductores de potencia y en ciertas topologías diodos y capacitores, que conmutan los distintos niveles de voltaje.

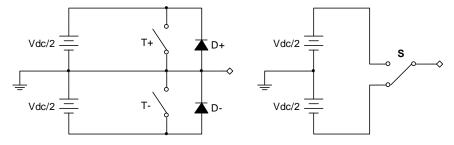

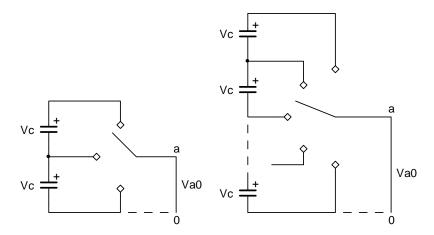

Una forma sencilla de entender la topología de un inversor, es la de dos interruptores de potencia mostrados en la Figura 1.3, en donde los interruptores son complementarios, al cerrar el interruptor superior a la carga llega un voltaje  $+V_{DC}/2$  y viceversa con lo que en la carga se genero una onda cuadrada de  $\pm V_{DC}/2$ , que ya es un tipo de inversor simple, entonces la topología es el arreglo de los interruptores con la fuente y los diodos.

Figura 1.3.: Inversor de medio puente y circuito equivalente.

Existen varias topologías de inversores multinivel, pero entre las más básica se encuentran:

- Convertidor con diodo enclavado (Diode-Clamped converter).

- Convertidor con capacitor flotante (Flying-Capacitor converter).

- Convertidor con conexión en cascada de puentes monofásicos (Cascaded Full-Bridge converter).

Pero también existe otras más que no son muy estudiadas ni utilizadas, algunas de ellas son:

- Convertidor asimétrico híbrido.

- Convertidor con topología multinivel en cascada.

- Inversores acoplados por transformador, entre otros.

#### 1.1.3.1. Conversor con diodo enclavado.

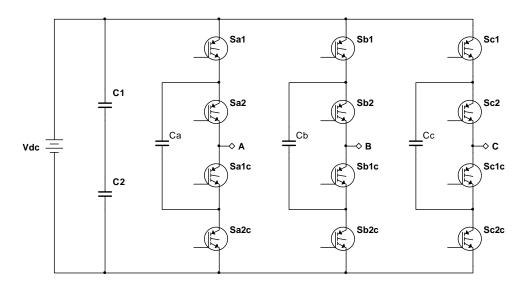

Los conversores de diodo enclavado (Diode Clamped), también conocidos como NPC o DCI, se caracterizan por que la fuente de tensión de continua se divide en la serie de niveles de tensión del inversor, por medio de puntos medios y/o intermedios creado por los condensadores y por el cierre de los interruptores, esto se puede observar en la Figura 1.4.

Figura 1.4.: Inversor de tres niveles NPC.

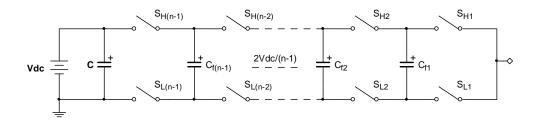

Para esta topología en número de condensadores necesarios para n niveles es igual a (n-1) condensadores, esto se puede observar en la Figura 1.5.

Figura 1.5.: Conversor NPC de 3 niveles y de n niveles

Las características principales de este tipo de topología son:

- Bajo número de condensadores.

- Tiene la ventaja de que necesita solo una fuente de alimentación.

- El sistema de control es más complicado cuando se incrementa el número de niveles, ya que el voltaje de los condensadores se desequilibra.

#### 1.1.3.2. Conversor con capacitor flotante

Esta topología también conocida como DCM, se dispone de una serie de condensadores flotantes los que permiten generar los distintos niveles de tensión esta topología, se puede ver en la Figura 1.6, los niveles se generan al conectar y desconectar ciertos condensadores, los mismos que están cargados con niveles de tensión diferentes y forman mallas, esto se puede ver en la Figura 1.7.

Las características principales de este tipo de topología son:

- Se necesita un número de condensadores mayor que la DCI.

- Tiene la ventaja de que necesita solo una fuente de alimentación.

- Existen una mayor cantidad de combinaciones en los interruptores para alcanzar el mismo nivel de salida.

- El sistema de control es más complicado cuando se incrementa el número de niveles, ya que el voltaje de los condensadores se desequilibra.

Figura 1.6.: Esquema de un inversor de tres niveles DMC.

Figura 1.7.: Mallas de condensadores del inversor DMC.

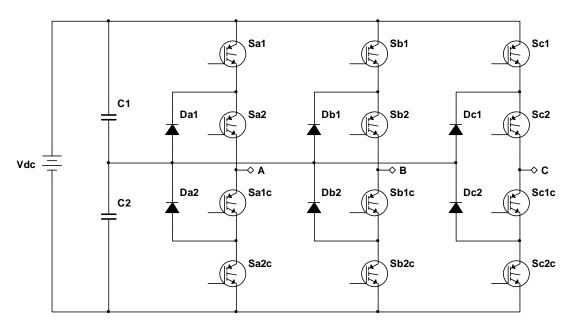

#### 1.1.3.3. Conversor con conexión en cascada de puente monofásico

En esta topología se usan varias fuentes independientes, se utiliza una fuente para generar dos niveles de tensión en la salida, y si se desean más niveles se conectan varias fuentes con sus interruptores en cascada como se muestra en la Figura 1.8, la tensión de salida es la suma de las tensiones de ingreso pudiéndose obtener cinco valores distintos: +2Vcc, +Vcc, 0, -Vcc, -2Vcc.

Al conectar varios puentes en conexión estrella se logran obtener un inversor trifásico como se muestra en la Figura 1.9.

Las características principales de este tipo de topología son:

- Se necesita un número mayor de fuentes de tensión independientes entre sí.

- Existen una mayor cantidad de combinaciones en los interruptores para alcanzar el mismo nivel de salida.

- El sistema de control no se complica tanto al incrementa el número de niveles, ya que el voltaje de las fuentes es más estable.

Gran capacidad de modularidad, ya que para aumentar o quitar niveles solo se necesita agregar fuentes e interruptores en cascada.

Figura 1.8.: Inversores monofásico en cascada

Figura 1.9.: Inversor trífasico en cascada

#### 1.1.3.4. Comparación entre las topologías básicas.

Las topologías básicas nos muestran distintas ventajas y desventajas entre ellas, pero la principal característica a tomar en cuenta es el número de componentes que utiliza, en la Tabla 1.1 se muestra una comparación de las distintas topologías, tomada de [6], en esta tabla se da el número de componentes por fase, siendo la topología en cascada la que menos requerimientos presenta.

| Configuración                     | DCM        | Condensador flotante | Cascada |

|-----------------------------------|------------|----------------------|---------|

| Interruptores principales         | 2(n-1)     | 2(n-1)               | 2(n-1)  |

| Diodos principales                | 2(n-1)     | 2(n-1)               | 2(n-1)  |

| Diodos de conexión                | (n-1)(n-2) | 0                    | 0       |

| Condensadores del bus de continua | (n-1)      | (n-1)                | (n-1)/2 |

| Condensadores de equilibrado      | 0          | (n-1)(n-2)/2         | 0       |

**Tabla 1.1.:** Comparación entre los requerimientos de componentes de las topologías básicas.

#### 1.1.4. Métodos de modulación para inversores multinivel.

Las técnicas de modulación para los algoritmos multinivel son programas o circuitos electrónicos que manejan a los semiconductores de potencia, para que enciendan o apaguen ciertos niveles del inversor para conseguir una forma de onda a la salida que se asemeje a la onda seno requerida.

Las técnicas de modulación son tan variadas, que van desde generar ondas cuadradas simples a la salida hasta técnicas basadas en técnicas de modulación vectorial espacial, las principales técnicas de modulación para inversores multinivel son las siguientes:

- Método de modulación SPWM.

- Métodos de modulación vectorial espacial.

En general la elección de un método u otro modulación depende de algunos factores entre ellos la frecuencia de conmutación de los interruptores, los recursos de hardware en cuanto al procesamiento del algoritmo y la finalidad del sistema, esto por el contenido de armónicos en la salida del sistema.

#### 1.1.4.1. Modulación SPWM

**Descripción.** La modulación SPWM o PWM senoidal, se basa en la comparar una onda senoidal llamada moduladora, de frecuencia fundamental (fr) con otra triangular o diente de sierra llamada portadora con frecuencia (fc), la misma que es mucho mayor a la moduladora, si en un instante de tiempo la portadora es mayor a la moduladora se enciende un interruptor de potencia de esa fase, esto se puede ver en la Figura 1.10. Al variar la magnitud de la moduladora  $A_r$ , varían los anchos de pulso que van a los interruptores de potencia y su indice de modulación  $m_a$ , con lo que se regula el voltaje RMS a la salida.

$$m_a = \frac{A_r}{A_c} \tag{1.1}$$

Donde:

$m_a$ : índice de modulación.

$A_r$ : amplitud de la onda moduladora.

$A_c$ : amplitud de la onda portadora.

Figura 1.10.: Onda senoidal moduladora y triangular portadora

Al variar la frecuencia de la onda moduladora, se varia la frecuencia de la onda de salida del sistema, y la relación de frecuencia  $m_f$ .

$$m_f = \frac{f_c}{f_r} \tag{1.2}$$

Donde:

$m_f$ : relación de frecuencias.

$f_r$ : frecuencia de la onda moduladora.

$f_c$ : frecuencia de la onda portadora.

Modulación SPWM multinivel. La modulación SPWM multinivel tiene el mismo principio que la SPWM simple presentada en la sección anterior con la diferencia que se cuenta con más de una portadora la misma por cada moduladora como se muestra en la Figura 1.11.

En ocasiones a las portadoras se las desfase 180° para que el contenido armónico baje y mejora la salida.

Para número n de niveles, es necesario un número (n-1) de portadoras.

Figura 1.11.: Ondas senoidal moduladora y triangulares portadoras para inversores multinivel

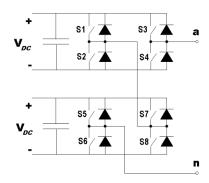

#### 1.1.4.2. Método de modulación vectorial espacial (SVM).

**Descripción.** Esta técnica de modulación se basa en obtener la secuencia de disparos de los interruptores de potencia a partir de una terna de valores [a,b,c] que son voltajes de referencia de un sistema trifásico, que por medio de la transformada d-q se transforma a un vector de referencia  $U_{ref}$  proporcional a la terna de valores trífasico, que giran en un plano a la misma frecuencia que se desea obtener a la salida.

El objetivo de esta transformación, es que a partir del vector de referencia en un tiempo de muestreo  $T_m$ , se obtenga la conmutación de los estados del inversor más cercanos, que también fueron transformados como se ve en la Figura 1.12, al vector de referencia los mismos que se encienden durante un tiempo menor o igual a  $T_m$ , dando como resultado que al sumarse sus contribuciones nos den un valor igual al vector de referencia, de la siguiente manera.

$$U_{ref} \cdot T_m = U_{E1} \cdot t_1 + U_{E2} \cdot t_2 + U_{E3} \cdot t_3 \tag{1.3}$$

$$t_1 + t_2 + t_3 = T_m (1.4)$$

Figura 1.12.: Espacio vectorial de un inversor de 4 niveles

En el algoritmo el vector de referencia  $U_{ref}$  es constante durante el tiempo de conmutación  $T_m$  y es igual a la suma de los vectores de referencia por el tiempo en el que permanecen activos los mismos.

Esta técnica de modulación presenta serias ventajas con respectos a la técnica SPWM, ya que según el circuito de control y la topología elegida se pueden minimizar las conmutaciones al igual que el contenido armónico de la señal de salida.

#### 1.1.5. Métodos de modulación vectorial espacial.

En cuanto a los métodos de modulación vectorial espacial existen muchos que se basan desde consideraciones geométricas, pasando por métodos iterativos hasta métodos trigonométricos, a continuación se enumeran algunos de ellos:

Algoritmo de modulación iterativo descrito en [6], que divide al espacio vectorial en 6 sextantes y estos en triángulos, para luego buscar en que triángulo se encuentra el vector referencia, para a partir de este calcular los tiempos de conmutación.

- Algoritmo de modulación basado en consideraciones geométricas descrito en [6], con bases en el algoritmo de modulación iterativo, que transforma el espacio vectorial en un rombo achatado y a partir de consideraciones geométricas generadas por el achatamiento del espacio vectorial se encuentra el triángulo en el que se encuentra el vector de referencia y los tiempos de conmutación.

- Algoritmo con bases trigonométricas como el descrito en [9], en donde por medio del calculo del angulo del vector de referencia se establecen los tiempos de conmutación, pero debido al uso de funciones trigonométricas su implementación es más difícil.

- Algoritmo de modulación vectorial 3D descritos en [10, 11] con una carga computacional mucho más grande que los anteriores.

En nuestro caso elegimos el algoritmo de modulación basado en consideraciones geométricas, debido a su baja carga computacional y fácil implementación en un sistema basado en FPGA.

# 1.2. Ventajas y desventajas de los métodos de modulación vectorial espacial.

Los métodos de modulación vectorial espacial tienen varias ventajas y desventajas frente a los métodos de SPWM, al igual que ventajas entre ellos mismos, a continuación se enumeran algunos:

La ventaja principal entre los métodos de modulación vectorial espacial frente los métodos SPWM, es que los SVM llegan a tener un menor indice de THD, pero con la desventaja que el sistema de control para el SVM es mucho más complejo, ya que el mismo necesita el calculo de tiempos de conmutación y estado a partir de un vector de referencia transformado de los componentes trifásicos en un tiempo dado, pero debido a los bajos costos de los DSP y FPGA en donde se pueden implementar estos algoritmos, esta desventajas esta desapareciendo.

En cambio entre los distintos algoritmos de modulación vectorial espacial existen varias ventajas y desventajas entre los mismos las mismas que son numeradas a continuación:

Algoritmo de modulación iterativo mencionado anteriormente, tiene la ventaja que es aplicable para cualquier número de niveles, pero el vector de referencia tiene que ser transportado al primer sextante para calcular los estados y luego al sextante de origen para calcular los tiempos, y al ser un algoritmo iterativo necesita una lógica secuencial para su implementación, por lo que su velocidad de procesamiento se puede ver comprometida si el número de niveles es muy grande o el sistema de control es muy lento.

- Algoritmo de modulación basado en consideraciones geométricas descrito en [6], al igual que el anterior es aplicable para cualquier número de niveles, y su carga computacional es independiente del número de niveles, es decir que es la misma para cualquier número de niveles, y su mayor ventaja es que no necesita el calculo de funciones trigonométricas para se implementación, que en el caso de implementar en FPGA es una gran ventaja ya que su descripción se simplifica.

- Algoritmo con bases trigonométricas como el descrito en [9], tiene desventajas con respecto a los anteriores, porque necesita el calculo de funciones trigonométricas para localizar la posición del vector de referencia, los estados y el tiempo de conmutación, que en el caso ser implementados en FPGA, su descripción se hace más difícil y los recursos necesarios del mismo son mayores.

- Algoritmo de modulación vectorial 3D descritos en [10, 11] tienen una carga computacional mucho más grande que los anteriores, pero con la ventaja que se pueden generar estados de conmutación con la señal fundamental sumada a armónicos que en ciertas aplicaciones pueden ser de gran utilidad.

#### 2. Diseño del sistema de control.

#### 2.1. Modulación vectorial espacial elegido.

#### 2.1.1. Introducción.

Los sistemas de control para inversores multinivel o convencionales, pueden ser de tipo analógicos, digitales o una mezcla de los dos dependiendo del tipo de modulación elegido para su control y los recursos con los que se cuenten para la realización del mismo, pero en general lo que se busca es reducir estos circuitos ya sea reduciendo las cargas computacionales en los sistemas de control o su circuito de control.

En el caso de los inversores, ya sean multinivel o convencionales, con un método de modulación vectorial espacial la mejor opción son sistemas digitales, por la facilidad de implementación de los algoritmos que los gobiernan, en sistemas basados en FPGA o DSP ya que los mismos permiten realizar modificaciones en su programación o comportamiento sin que sus conexiones externas requieran cambios, al igual que su tamaño reducido y gran capacidad, son la mejor opción como se menciona en [12, 8, 7, 13, 6].

Los métodos de modulación vectorial espacial se basan en la consideración que la terna [a,b,c] de voltajes en un instante de tiempo, se pueden transformar a un sistema d-q de un vector de magnitud proporcional al voltaje de la terna y de frecuencia de giro igual a la frecuencia de la terna, a esto se le conoce como transformada de Park, a partir de este vector se calculan las conmutaciones necesarias del sistema.

#### 2.1.2. Transformada de Park.

La transformada de Park, conocida también como transformada d-q es un método usado para convertir los componente [a,b,c] de un sistema trifásico senoidal a un sistema [0,d,q]. Esto se consigue multiplicado el vector trifásico [a,b,c] por una matriz de transformación [T] como se muestran en la siguiente expresión.

$$v_{0dq}^r = R(\theta_r) \cdot P(0) \cdot v_{abc} \tag{2.1}$$

Donde:

$v_{abc}$  = vector del sistema trifásico senoidal.

$\boldsymbol{v}^r_{0dq} = \text{vector del sistema transformado.}$

$R(\theta_r) = \text{matriz}$  de transformación a un sistema coordenado giratorio denominado d-q.

P(0)= matriz de transformación a un sistema coordenado estacionario denominado  $\alpha\beta$ .

#### 2.1.2.1. Transformación a un sistema de referencia estacionario.

La transformación a un sistema de referencia estacionario o transformada de Clark es multiplicar el vector de voltajes [a,b,c] por la matriz de transformación P(0) mostrada en la siguiente expresión, que da como resultado ejes 0,  $\alpha$  y  $\beta[14]$ .

$$P(0) = \frac{2}{3} \cdot \begin{bmatrix} \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \\ 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & -\frac{\sqrt{2}}{3} & \frac{\sqrt{2}}{3} \end{bmatrix}$$

(2.2)

En algunos documentos reemplazan  $\frac{2}{3}$ , con  $\sqrt{\frac{2}{3}}$  es por que se asume que son valores pico de voltaje[15].

$$v_{0\alpha\beta} = P(0) \cdot v_{abc} \tag{2.3}$$

En algunos casos se asume que el sistema de referencia estacionario dado por  $v_{0\alpha\beta}$  es directamente el valor de la transformada de Park.

$$v_{\alpha} = v_d = \frac{1}{3} \cdot (2v_a - v_b - v_c) \tag{2.4}$$

$$v_{\beta} = v_q = \frac{1}{\sqrt{3}} \cdot (v_b - v_c) \tag{2.5}$$

En el caso de ser un sistema de componentes simétricos el valor de  $v_0$  es igual a cero.

Figura 2.1.: Transformada de Clark [1].

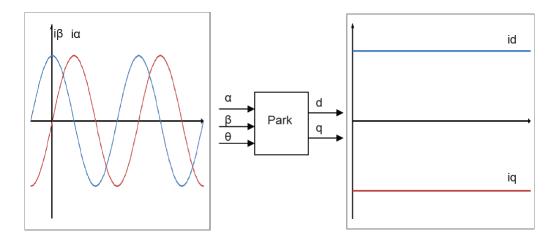

#### 2.1.2.2. Transformación a un sistema de referencia giratorio.

La transformación a un sistema de referencia giratorio es multiplicar el vector transformado a un sistema estacionario por la matriz de transformación  $R(\theta_r)$  mostrada en la siguiente expresión, que da como resultado ejes 0, d y q[14].

$$R(\theta_r) = \begin{bmatrix} 1 & 0 & 0 \\ 0 & \cos(\theta_r) & -\sin(\theta_r) \\ 0 & \sin(\theta_r) & \cos(\theta_r) \end{bmatrix}$$

(2.6)

$$v_{0dq} = P(\theta_r) \cdot v_{0\alpha\beta} \tag{2.7}$$

Figura 2.2.: Transformada de Park [1].

Combinando ambas matrices en una sola, la matriz de transformación queda como se muestra en la siguiente expresión:

$$P(\theta_r) = R(\theta_r) \cdot P(0) \tag{2.8}$$

$$v_{0dq}^{r} = P\left(\theta_{r}\right) \cdot v_{abc} \tag{2.9}$$

$$\begin{bmatrix} v_0^r \\ v_d^r \\ v_q^r \end{bmatrix} = \frac{2}{3} \cdot \begin{bmatrix} \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \\ \cos(\theta_r) & \cos(\theta_r - \frac{2\pi}{3}) & \cos(\theta_r + \frac{2\pi}{3}) \\ \sin(\theta_r) & \sin(\theta_r - \frac{2\pi}{3}) & \sin(\theta_r + \frac{2\pi}{3}) \end{bmatrix} \cdot \begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix}$$

(2.10)

# 2.1.3. Método de modulación vectorial de consideraciones geométricas.

#### 2.1.3.1. Introducción.

Este método de modulación descrito en [6], nos brinda la posibilidad de implementarlo en DSP o FPGA fácilmente debido principalmente a que su carga computacional es pequeña y otra ventaja que muestra es que se puede implementar para cualquier número de niveles, sin que su complejidad aumente y sin la necesidad de almacenar datos en memorias o tablas para su procesamiento.

#### 2.1.3.2. Descripción del algoritmo.

Este algoritmo de modulación busca generar una secuencia de conmutación en cada tiempo de muestreo  $T_m$ , estableciendo cuales son los niveles a usar y los tiempos en los cuales permanecen activos.

#### Paso 1: Normalizar el vector de referencia.

La entrada del algoritmo es un vector de tensión normalizado u\*, que depende del número de niveles y de la tensión de la fuente o los condensadores, y sus componentes en el plano d-q vienen dadas por la siguiente expresión.

$$u* = \begin{bmatrix} v_d^{v_a v_b v_c} \\ v_q^{v_a v_b v_c} \end{bmatrix} = \frac{1}{3} \cdot \frac{n-1}{V_{DC}} \cdot \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \cdot \begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix}$$

(2.11)

Donde:

$v_d^{E_aE_bE_c}=$  Componente d<br/> del vector de referencia normalizado.

$v_q^{E_aE_bE_c}=$  Componente q del vector de referencia normalizado.

n = número de niveles del inversor.

$V_{DC}$  = Tensión de la fuente o de los condensadores.

$v_a, v_b, v_c =$  Vector de tensiones pico del sistema trifásico senoidal en un tiempo.

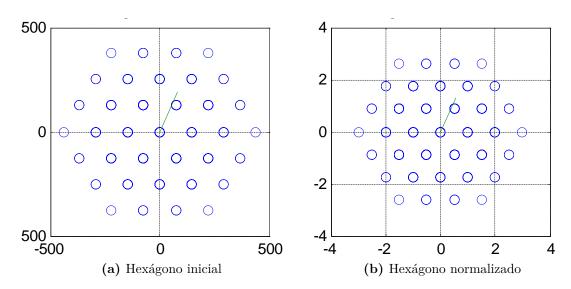

En si lo que se hizo fue transformar de un sistema trifásico senoidal a uno estacionario por medio de la matriz de Clark y a esto normalizarlo para su procesamiento, en la Figura 2.3 se puede ver el resultado de la transformación y normalización de un inversor de 4 niveles, lo mismo se hizo con los niveles del inversor.

Figura 2.3.: Hexágonos normales y normalizados

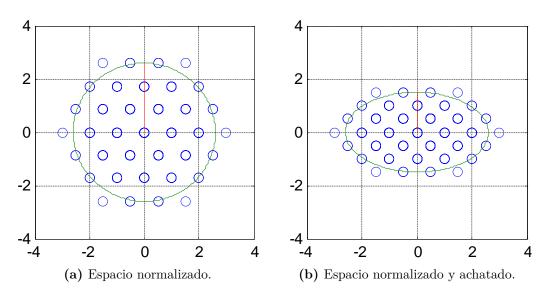

## Paso 2: Achatar el espacio vectorial.

El siguiente paso es multiplicar a la parte imaginaria (componente q) del vector de referencia u\*y de los niveles del inversor por  $1/\sqrt{3}$ , con lo que los estados que inicialmente se encuentran a 60° queden a 45° y se elimine la necesidad del cálculo de ángulos y funciones trigonométricas y faciliten los cálculos del tiempo y los estados a conmutar.

$$u*_{tranformado} = Re \{u*\} + j\frac{1}{\sqrt{3}}Im \{u*\}$$

(2.12)

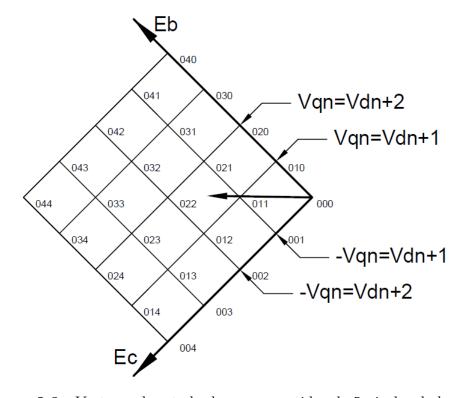

Hecho esto en el hexágono achatado cada nivel del inversor queda representado por el valor de una terna  $[E_a, E_b, E_c]$  y dividido en 3 zonas como se ve en la Figura 2.4.

Figura 2.4.: Espacio de estados normalizados

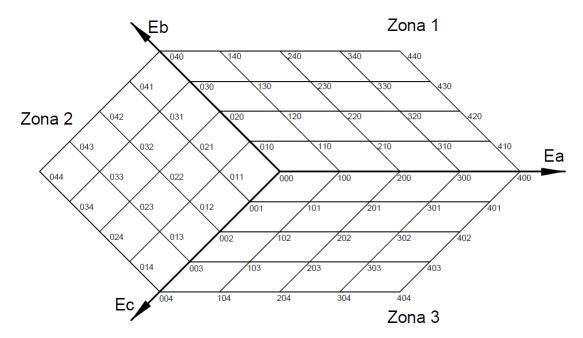

## Paso 3: Elección de la zona en la que se encuentra el vector de referencia.

Ahora debemos establecer la zona en la que se encuentra el vector de referencia transformado, las zonas se indica en la Figura 2.5.

Figura 2.5.: Zonas del plano achatado.

La elección de la zona se lo hace por comparación entre la parte real e imaginaria del vector de referencia transformado, la forma de establecerlo se muestra en el flujograma de la Figura 2.6.

**Figura 2.6.:** Flujograma para determinar la zona en la que se encuentra el vector de referencia.

## Paso 4: Cálculo de las coordenadas del vértice de un sector triangular.

El siguiente paso es encontrar el vértice del sector en el que se encuentra el vector de referencia, este vértice debe ser lo más próximo al origen del espacio vectorial.

Como ya se menciono anteriormente las coordenadas  $[E_a, E_b, E_c]$  representan un nivel del inversor y a partir de esto se calcula el vértice.

#### Zona 1:

Cualquier vector localizado entre las lineas paralelas inclinadas mostradas en la Figura 2.7 debe cumplir la siguiente inecuación:

$$-v_{dn} + 1 < v_{qn} < -v_{dn} + 2 (2.13)$$

$$1 < v_{an} + v_{dn} < 2 \tag{2.14}$$

Entonces el valor del vértice para este vector en el eje  $E_a$  siempre es igual a uno a lo largo de las lineas paralelas inclinadas, con lo que el valor del vértice en el

eje  $E_a$  es igual a:

$$E_a = Parte\,entera\,(v_{dn} + v_{qn}) \tag{2.15}$$

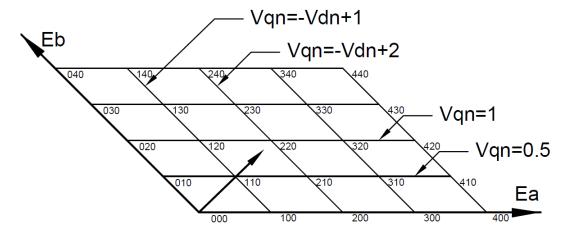

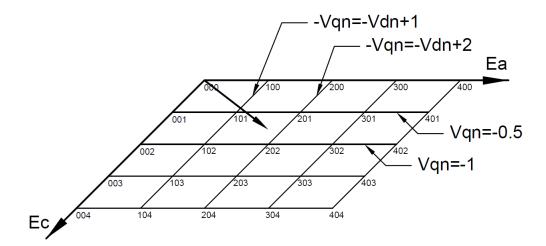

Figura 2.7.: Vectores de estado de un convertidor de 5 niveles de la zona 1.

Cualquier vector localizado entre las lineas paralelas horizontales mostradas en la Figura 2.7 debe cumplir la siguiente inecuación:

$$0, 5 < v_{qn} < 1 \tag{2.16}$$

$$1 < v_{qn} < 2$$

(2.17)

Entonces el valor del vértice para este vector en el eje  $E_b$  siempre es igual a uno a lo largo de las lineas paralelas horizontales, con lo que el valor del vértice en el eje  $E_b$  es igual a:

$$E_b = Parte\ entera\ (2 \cdot v_{gn}) \tag{2.18}$$

Y el valor en el eje  $E_c$  en este zona es igual a 0.

## Zona 2:

Cualquier vector localizado entre las lineas paralelas inclinadas perpendiculares al eje  $E_b$  mostradas en la Figura 2.8 debe cumplir la siguiente inecuación:

$$v_{dn} + 1 < v_{qn} < v_{dn} + 2 \tag{2.19}$$

$$1 < v_{qn} - v_{dn} < 2 \tag{2.20}$$

Entonces el valor del vértice para este vector en el eje  $E_b$  siempre es igual a uno a lo largo de las lineas paralelas inclinadas perpendiculares a este eje, con lo que el valor del vértice en el eje  $E_b$  es igual a:

$$E_b = Parte\,entera\,(-v_{dn} + v_{qn}) \tag{2.21}$$

Figura 2.8.: Vectores de estado de un convertidor de 5 niveles de la zona 2.

Cualquier vector localizado entre las lineas paralelas inclinadas perpendiculares al eje  $E_c$  mostradas en la Figura 2.8 debe cumplir la siguiente inecuación:

$$v_{dn} + 1 < -v_{qn} < v_{dn} + 2 \tag{2.22}$$

$$1 < -v_{qn} - v_{dn} < 2 \tag{2.23}$$

Entonces el valor del vértice para este vector en el eje  $E_c$  siempre es igual a uno a lo largo de las lineas paralelas inclinadas perpendiculares a este eje, con lo que el valor del vértice en el eje  $E_c$  es igual a:

$$E_c = Parte\,entera\,(-v_{dn} - v_{qn}) \tag{2.24}$$

Y el valor en el eje  $E_a$  en este zona es igual a 0.

#### Zona 3:

Cualquier vector localizado entre las lineas paralelas e inclinadas mostradas en la Figura 2.9 debe cumplir la siguiente inecuación:

$$-v_{dn} + 1 < -v_{qn} < -v_{dn} + 2 (2.25)$$

$$1 < -v_{on} + v_{dn} < 2 \tag{2.26}$$

Entonces el valor del vértice para este vector en el eje  $E_a$  siempre es igual a uno a lo largo de las lineas paralelas inclinadas, con lo que el valor del vértice en el eje  $E_a$  es igual a:

$$E_a = Parte\,entera\,(v_{dn} - v_{qn}) \tag{2.27}$$

Figura 2.9.: Vectores de estado de un convertidor de 5 niveles de la zona 3.

Cualquier vector localizado entre las lineas paralelas horizontales mostradas en la Figura 2.9 debe cumplir la siguiente inecuación:

$$-0, 5 > v_{qn} > -1 \tag{2.28}$$

$$-1 > v_{qn} > -2 \tag{2.29}$$

Entonces el valor del vértice para este vector en el eje  $E_c$  siempre es igual a uno a lo largo de las lineas paralelas horizontales, con lo que el valor del vértice en el eje  $E_c$  es igual a:

$$E_c = Parte\,entera\,(-2 \cdot v_{qn}) \tag{2.30}$$

Y el valor en el eje  $E_b$  en este zona es igual a 0.

# Paso 5: Orientación del sector triangular

Una vez determinado el vértice del sector en donde se encuentra el vector de referencia como se describió en el paso anterior, el siguiente paso es dividir al sector en dos sectores triangulares y encontrar en que sector triangular se encuentra el vector de referencia.

Lo primero que hace es transformar el estado vértice mediante la transformada de Park descrita anteriormente donde.

$$\begin{bmatrix} e_{dn}^{E_a, E_b, E_c} \\ e_{qn}^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} e_d^{E_a, E_b, E_c} \\ \frac{1}{\sqrt{3}} e_q^{E_a, E_b, E_c} \end{bmatrix}$$

(2.31)

Siendo:

$$\begin{bmatrix} e_d^{E_a, E_b, E_c} \\ e_q^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix}$$

(2.32)

Por lo tanto:

$$\begin{bmatrix} e_{dn}^{E_a, E_b, E_c} \\ e_{qn}^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix}$$

(2.33)

#### Zona 1:

Calculamos el valor del vértice del sector en donde se encuentra el vector de referencia.

$$\begin{bmatrix} e_{dn}^{E_a, E_b, E_c} \\ e_{qn}^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix}$$

(2.34)

$$e_{dn}^{E_a, E_b, E_c} = E_a - \frac{E_b}{2} \tag{2.35}$$

$$e_{qn}^{E_a, E_b, E_c} = \frac{E_b}{2} \tag{2.36}$$

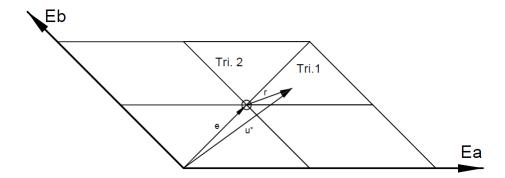

Como se ve en la Figura 2.10 al vector de referencia  $\vec{u*}$  es igual a la suma del vector  $\vec{e_{qn}}$  que apunta al vértice del vector de referencia, más un vector  $\vec{r}$ , por lo tanto

$$\vec{r} = \vec{u} \cdot \vec{r} - \vec{e_{qn}} = v_{dn} + j(v_{qn}) - \left[ \left( E_a - \frac{E_b}{2} \right) + j\left( \frac{E_b}{2} \right) \right]$$

(2.37)

Separando la parte real e imaginaria.

$$Re\left\{\vec{r}\right\} = v_{dn} - \left(E_a - \frac{E_b}{2}\right) \tag{2.38}$$

$$Im\left\{\vec{r}\right\} = v_{qn} - \left(\frac{E_b}{2}\right) \tag{2.39}$$

Figura 2.10.: Región geométrica en la zona 1.

Ahora el vector  $\vec{r}$  se encuentra en el triangulo 1 si su parte real es mayor o igual a la imaginaria con lo que:

$$Im\{\vec{r}\} \le Re\{\vec{r}\} \implies v_{qn} - \left(\frac{E_b}{2}\right) \le v_{dn} - \left(E_a - \frac{E_b}{2}\right)$$

(2.40)

Entonces resolviendo esta inecuación nos da como resultado que el vector  $\vec{u*}$  se encuentra en triangulo 1 cuando:

$$v_{qn} - v_{dn} \le -E_a + E_b \tag{2.41}$$

Por lo tanto se encuentra en el triangulo 2 cuando:

$$v_{qn} - v_{dn} > -E_a + E_b \tag{2.42}$$

## Zona 2:

Calculamos el valor del vértice del sector en donde se encuentra el vector de referencia.

$$\begin{bmatrix} e_{dn}^{E_a, E_b, E_c} \\ e_{qn}^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix}$$

(2.43)

$$e_{dn}^{E_a, E_b, E_c} = -\frac{E_b}{2} - \frac{E_c}{2} \tag{2.44}$$

$$e_{qn}^{E_a, E_b, E_c} = \frac{E_b}{2} - \frac{E_c}{2} \tag{2.45}$$

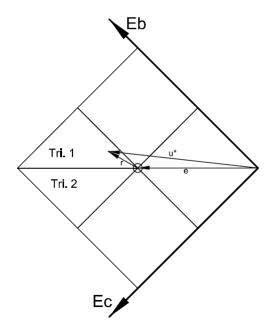

Como se ve en la Figura 2.11 al vector de referencia  $\vec{u*}$  es igual a la suma del vector  $\vec{e_{qn}}$  que apunta al vértice del vector de referencia, más un vector  $\vec{r}$ , por lo tanto

$$\vec{r} = \vec{u} * - \vec{e_{qn}} = v_{dn} + j(v_{qn}) - \left[ \left( -\frac{E_b}{2} - \frac{E_c}{2} \right) + j\left( \frac{E_b}{2} - \frac{E_c}{2} \right) \right]$$

(2.46)

Separando la parte real e imaginaria.

$$Re\{\vec{r}\} = v_{dn} - \left(-\frac{E_b}{2} - \frac{E_c}{2}\right)$$

(2.47)

$$Im\{\vec{r}\} = v_{qn} - \left(\frac{E_b}{2} - \frac{E_c}{2}\right)$$

(2.48)

Figura 2.11.: Región geométrica en la zona 2.

Ahora el vector  $\vec{r}$  se encuentra en el triangulo si su parte imaginaria es mayor o igual a cero con lo que:

$$Im\{\vec{r}\} \ge 0 \implies v_{qn} - \left(\frac{E_b}{2} - \frac{E_c}{2}\right) \ge 0$$

(2.49)

Entonces resolviendo esta inecuación nos da como resultado que el vector  $\vec{u*}$  se encuentra en triangulo 1 cuando:

$$2v_{qn} \ge E_b - E_c \tag{2.50}$$

Por lo tanto se encuentra en el triangulo 2 cuando:

$$2v_{qn} < E_b - E_c \tag{2.51}$$

#### Zona 3:

Calculamos el valor del vértice del sector en donde se encuentra el vector de referencia.

$$\begin{bmatrix} e_{dn}^{E_a, E_b, E_c} \\ e_{qn}^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix}$$

(2.52)

$$e_{dn}^{E_a, E_b, E_c} = E_a - \frac{E_c}{2} \tag{2.53}$$

$$e_{qn}^{E_a, E_b, E_c} = -\frac{E_c}{2} \tag{2.54}$$

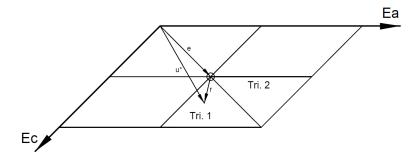

Como se ve en la Figura 2.12 al vector de referencia  $\vec{u*}$  es igual a la suma del vector  $\vec{e_{qn}}$  que apunta al vértice del vector de referencia, más un vector  $\vec{r}$ , por lo tanto

$$\vec{r} = \vec{u} \cdot \vec{r} - \vec{e_{qn}} = v_{dn} + j(v_{qn}) - \left[ \left( E_a - \frac{E_c}{2} \right) + j \left( -\frac{E_c}{2} \right) \right]$$

(2.55)

Separando la parte real e imaginaria.

$$Re\left\{\vec{r}\right\} = v_{dn} - \left(E_a - \frac{E_c}{2}\right) \tag{2.56}$$

$$Im\left\{\vec{r}\right\} = v_{qn} + \left(\frac{E_c}{2}\right) \tag{2.57}$$

Figura 2.12.: Región geométrica en la zona 3.

Ahora el vector  $\vec{r}$  se encuentra en el triangulo 1 si su parte real es menor o igual a menos su parte imaginaria con lo que:

$$-Im\left\{\vec{r}\right\} \ge Re\left\{\vec{r}\right\} \qquad \Longrightarrow \qquad -\left[v_{qn} + \left(\frac{E_c}{2}\right)\right] \ge v_{dn} - \left(E_a - \frac{E_c}{2}\right) \tag{2.58}$$

Entonces resolviendo esta inecuación nos da como resultado que el vector  $\vec{u*}$  se encuentra en triangulo 1 cuando:

$$v_{qn} + v_{dn} \le E_a - E_c \tag{2.59}$$

Por lo tanto se encuentra en el triangulo 2 cuando:

$$v_{qn} + v_{dn} > -E_a - E_c \tag{2.60}$$

#### Paso 6: Cálculo de los tres vectores más cercanos al vector de referencia

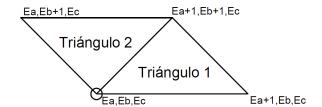

Una vez conocido el vértice  $[E_a, E_b, E_c]$  y la orientación del sector triangular en donde se encuentra el vector de referencia, establecer los estados de conmutación es fácil como se muestra a continuación:

## Zona 1:

Sector triangular 1:

Estado 1 :

$$E_a, E_b, E_c$$

; Estado 2 :  $E_a+1, E_b, E_c$ ; Estado 3 :  $E_a+1, E_b+1, E_c$  (2.61)

Sector triangular 2:

Estado 1:

$$E_a, E_b, E_c$$

; Estado 2:  $E_a+1, E_b+1, E_c$ ; Estado 3:  $E_a, E_b+1, E_c$  (2.62)

Figura 2.13.: Coordenadas de los niveles del inversor de la zona 1.

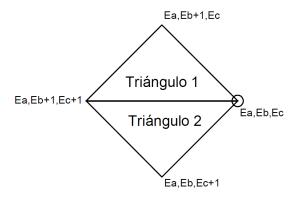

## Zona 2:

Sector triangular 1:

Estado 1:

$$E_a, E_b, E_c$$

; Estado 2:  $E_a, E_b+1, E_c+1$ ; Estado 3:  $E_a, E_b+1, E_c$  (2.63)

Sector triangular 2:

Estado 1:

$$E_a, E_b, E_c$$

; Estado 2:  $E_a, E_b, E_c+1$ ; Estado 3:  $E_a, E_b+1, E_c+1$  (2.64)

Figura 2.14.: Coordenadas de los niveles del inversor de la zona 2.

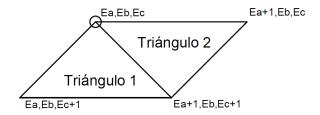

#### Zona 3:

Sector triangular 1:

Estado 1:

$$E_a, E_b, E_c$$

; Estado 2:  $E_a, E_b, E_c+1$ ; Estado 3:  $E_a+1, E_b, E_c+1$  (2.65)

Sector triangular 2:

Estado 1:

$$E_a, E_b, E_c$$

; Estado 2:  $E_a+1, E_b, E_c+1$ ; Estado 3:  $E_a+1, E_b, E_c$  (2.66)

Figura 2.15.: Coordenadas de los niveles del inversor de la zona 3.

#### Paso 7: Cálculo de los tiempos de conmutación de los vectores activos.

La ventaja que presenta este algoritmo es la facilidad del calculo de los tiempos de conmutación, ya que el mismo se realiza por simple adición de la parte real e imaginaria del vector de referencia de tensión y las componentes  $E_a$ ,  $E_b$ , y  $E_c$ .

El calculo de tiempos se basa en la trasformación de Park descrita anteriormente donde.

$$\begin{bmatrix} v_{dn}^{E_a, E_b, E_c} \\ v_{qn}^{E_a, E_b, E_c} \end{bmatrix} = \begin{pmatrix} v_d^{E_a, E_b, E_c} \\ \frac{1}{\sqrt{3}} v_q^{E_a, E_b, E_c} \end{pmatrix}$$

(2.67)

Siendo:

$$\begin{bmatrix} v_d^{E_a, E_b, E_c} \\ v_q^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix}$$

(2.68)

Por lo tanto:

$$\begin{bmatrix} v_{dn}^{E_a, E_b, E_c} \\ v_{qn}^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix}$$

(2.69)

Entonces los pasos a seguir, es sumar la contribución de las parte real e imaginaria de los tres vectores activos generados por el vector de referencia en un tiempo, y que esto sea igual a la parte real  $v_{dn}$  e imaginaria  $v_{qn}$  del vector de referencia en un tiempo igual a 1, de la siguiente manera:

#### Zona 1:

#### Sector triangular 1:

Estado 1: en donde permanece activo durante un tiempo 1.

$$\begin{bmatrix} v_{dn}^{E_a, E_b, E_c} \\ v_{qn}^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix}$$

(2.70)

$$v_{dn}^{E_a, E_b, E_c} = E_a - \frac{E_b}{2} \tag{2.71}$$

$$v_{qn}^{E_a, E_b, E_c} = \frac{E_b}{2} \tag{2.72}$$

Estado 2: en donde permanece activo durante un tiempo 2.

$$\begin{bmatrix} v_{dn}^{E_a+1,E_b,E_c} \\ v_{qn}^{E_a+1,E_b,E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a+1 \\ E_b \\ E_c \end{bmatrix}$$

(2.73)

$$v_{dn}^{E_a+1,E_b,E_c} = E_a + 1 - \frac{E_b}{2} \tag{2.74}$$

$$v_{qn}^{E_a+1,E_b,E_c} = \frac{E_b}{2} \tag{2.75}$$

Estado 3: en donde permanece activo durante un tiempo 3.

$$\begin{bmatrix} v_{dn}^{E_a+1,E_b+1,E_c} \\ v_{qn}^{E_a+1,E_b+1,E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a+1 \\ E_b+1 \\ E_c \end{bmatrix}$$

(2.76)

$$v_{dn}^{E_a+1,E_b+1,E_c} = E_a + 1 - \frac{E_b+1}{2} = E_a - \frac{E_b}{2} + \frac{1}{2}$$

(2.77)

$$v_{qn}^{E_a+1,E_b+1,E_c} = \frac{E_b+1}{2} \tag{2.78}$$

Entonces sumamos las aportaciones de las distintos niveles y nos da:

$$v_{dn} \cdot 1 = \left(v_{dn}^{E_a, E_b, E_c}\right) t_1 + \left(v_{dn}^{E_a + 1, E_b, E_c}\right) t_2 + \left(v_{dn}^{E_a + 1, E_b + 1, E_c}\right) t_3 \tag{2.79}$$

$$v_{dn} = \left(E_a - \frac{E_b}{2}\right)t_1 + \left(E_a - \frac{E_b}{2} + 1\right)t_2 + \left(E_a - \frac{E_b}{2} + \frac{1}{2}\right)t_3 \tag{2.80}$$

$$v_{qn} \cdot 1 = \left(v_{qn}^{E_a, E_b, E_c}\right) t_1 + \left(v_{qn}^{E_a+1, E_b, E_c}\right) t_2 + \left(v_{qn}^{E_a+1, E_b+1, E_c}\right) t_3 \tag{2.81}$$

$$v_{qn} = \left(\frac{E_b}{2}\right)t_1 + \left(\frac{E_b}{2}\right)t_2 + \left(\frac{E_b + 1}{2}\right)t_3 \tag{2.82}$$

$$t_1 + t_2 + t_3 = 1 (2.83)$$

Resolviendo el sistema de ecuaciones generado por la Ecuación 2.80, Ecuación 2.82 y Ecuación 2.83, los tiempos de conmutación son:

$$t_1 = 1 + E_a - v_{dn} - v_{qn} (2.84)$$

$$t_2 = -E_a + E_b + v_{dn} - v_{qn} (2.85)$$

$$t_3 = -E_b + v_{qn} (2.86)$$

#### Sector triangular 2:

Estado 1: en donde permanece activo durante un tiempo 1.

$$\begin{bmatrix} v_{dn}^{E_a, E_b, E_c} \\ v_{qn}^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix}$$

(2.87)

$$v_{dn}^{E_a, E_b, E_c} = E_a - \frac{E_b}{2} \tag{2.88}$$

$$v_{qn}^{E_a, E_b, E_c} = \frac{E_b}{2} \tag{2.89}$$

Estado 2: en donde permanece activo durante un tiempo 2.

$$\begin{bmatrix} v_{dn}^{E_a+1,E_b+1,E_c} \\ v_{qn}^{E_a+1,E_b+1,E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a+1 \\ E_b+1 \\ E_c \end{bmatrix}$$

(2.90)

$$v_{dn}^{E_a+1,E_b+1,E_c} = E_a + 1 - \frac{E_b+1}{2} = E_a - \frac{E_b}{2} + \frac{1}{2}$$

(2.91)

$$v_{qn}^{E_a+1,E_b+1,E_c} = \frac{E_b+1}{2} \tag{2.92}$$

Estado 3: en donde permanece activo durante un tiempo 3.

$$\begin{bmatrix} v_{dn}^{E_a, E_b + 1, E_c} \\ v_{qn}^{E_a, E_b + 1, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b + 1 \\ E_c \end{bmatrix}$$

(2.93)

$$v_{dn}^{E_a, E_b + 1, E_c} = E_a - \frac{E_b + 1}{2} = E_a - \frac{E_b}{2} - \frac{1}{2}$$

(2.94)

$$v_{qn}^{E_a, E_b + 1, E_c} = \frac{E_b + 1}{2} \tag{2.95}$$

Entonces sumamos las aportaciones de las distintos niveles y nos da:

$$v_{dn} \cdot 1 = \left(v_{dn}^{E_a, E_b, E_c}\right) t_1 + \left(v_{dn}^{E_a + 1, E_b + 1, E_c}\right) t_2 + \left(v_{dn}^{E_a, E_b + 1, E_c}\right) t_3 \tag{2.96}$$

$$v_{dn} = \left(E_a - \frac{E_b}{2}\right)t_1 + \left(E_a - \frac{E_b}{2} + \frac{1}{2}\right)t_2 + \left(E_a - \frac{E_b}{2} - \frac{1}{2}\right)t_3 \tag{2.97}$$

$$v_{qn} \cdot 1 = \left(v_{qn}^{E_a, E_b, E_c}\right) t_1 + \left(v_{qn}^{E_a + 1, E_b + 1, E_c}\right) t_2 + \left(v_{qn}^{E_a, E_b + 1, E_c}\right) t_3 \tag{2.98}$$

$$v_{qn} = \left(\frac{E_b}{2}\right)t_1 + \left(\frac{E_b + 1}{2}\right)t_2 + \left(\frac{E_b + 1}{2}\right)t_3 \tag{2.99}$$

$$t_1 + t_2 + t_3 = 1 (2.100)$$

Resolviendo el sistema de ecuaciones generado por la Ecuación 2.97, Ecuación 2.99 y Ecuación 2.100, los tiempos de commutación son:

$$t_1 = 1 + E_b - 2v_{qn} (2.101)$$

$$t_2 = -E_a + v_{dn} + v_{qn} (2.102)$$

$$t_3 = E_a - E_b - v_{dn} + v_{gn} (2.103)$$

## Zona 2:

#### Sector triangular 1:

Estado 1: en donde permanece activo durante un tiempo 1.

$$\begin{bmatrix} v_{dn}^{E_a, E_b, E_c} \\ v_{qn}^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix}$$

(2.104)

$$v_{dn}^{E_a, E_b, E_c} = -\frac{E_b}{2} - \frac{E_c}{2} \tag{2.105}$$

$$v_{qn}^{E_a, E_b, E_c} = \frac{E_b}{2} - \frac{E_c}{2} \tag{2.106}$$

Estado 2: en donde permanece activo durante un tiempo 2.

$$\begin{bmatrix} v_{dn}^{E_a, E_b + 1, E_c + 1} \\ v_{qn}^{E_a, E_b + 1, E_c + 1} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b + 1 \\ E_c + 1 \end{bmatrix}$$

(2.107)

$$v_{dn}^{E_a,E_b+1,E_c+1} = -\frac{E_b+1}{2} - \frac{E_c+1}{2} = -\frac{E_b}{2} - \frac{E_c}{2} - 1$$

(2.108)

$$v_{qn}^{E_a,E_b+1,E_c+1} = \frac{E_b+1}{2} - \frac{E_c+1}{2} = \frac{E_b}{2} - \frac{E_c}{2}$$

(2.109)

Estado 3: en donde permanece activo durante un tiempo 3.

$$\begin{bmatrix} v_{dn}^{E_a, E_b + 1, E_c} \\ v_{qn}^{E_a, E_b + 1, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b + 1 \\ E_c \end{bmatrix}$$

(2.110)

$$v_{dn}^{E_a, E_b + 1, E_c} = -\frac{E_b + 1}{2} - \frac{E_c}{2} = -\frac{E_b}{2} - \frac{E_c}{2} - \frac{1}{2}$$

(2.111)

$$v_{qn}^{E_a, E_b + 1, E_c} = \frac{E_b + 1}{2} - \frac{E_c}{2} = \frac{E_b}{2} - \frac{E_c}{2} + \frac{1}{2}$$

(2.112)

Entonces sumamos las aportaciones de las distintos niveles y nos da:

$$v_{dn} \cdot 1 = \left(v_{dn}^{E_a, E_b, E_c}\right) t_1 + \left(v_{dn}^{E_a, E_b + 1, E_c + 1}\right) t_2 + \left(v_{dn}^{E_a, E_b + 1, E_c}\right) t_3 \tag{2.113}$$

$$v_{dn} = \left(-\frac{E_b}{2} - \frac{E_c}{2}\right)t_1 + \left(-\frac{E_b}{2} - \frac{E_c}{2} - 1\right)t_2 + \left(-\frac{E_b}{2} - \frac{E_c}{2} - \frac{1}{2}\right)t_3 \quad (2.114)$$

$$v_{qn} \cdot 1 = \left(v_{qn}^{E_a, E_b, E_c}\right) t_1 + \left(v_{qn}^{E_a, E_b + 1, E_c + 1}\right) t_2 + \left(v_{qn}^{E_a, E_b + 1, E_c}\right) t_3 \tag{2.115}$$

$$v_{qn} = \left(\frac{E_b}{2} - \frac{E_c}{2}\right)t_1 + \left(\frac{E_b}{2} - \frac{E_c}{2}\right)t_2 + \left(\frac{E_b}{2} - \frac{E_c}{2} + \frac{1}{2}\right)t_3 \tag{2.116}$$

$$t_1 + t_2 + t_3 = 1 (2.117)$$

Resolviendo el sistema de ecuaciones generado por la Ecuación 2.114, Ecuación 2.116 y Ecuación 2.117, los tiempos de conmutación son:

$$t_1 = 1 + E_b + v_{dn} - v_{qn} (2.118)$$

$$t_2 = -E_c - v_{dn} - v_{qn} (2.119)$$

$$t_3 = E_c - E_b + 2v_{qn} (2.120)$$

## Sector triangular 2:

Estado 1: en donde permanece activo durante un tiempo 1.

$$\begin{bmatrix} v_{dn}^{E_a, E_b, E_c} \\ v_{qn}^{E_a, E_b, E_c} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{1}{2} & -\frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} E_a \\ E_b \\ E_c \end{bmatrix}$$

(2.121)

$$v_{dn}^{E_a, E_b, E_c} = -\frac{E_b}{2} - \frac{E_c}{2} \tag{2.122}$$

$$v_{qn}^{E_a, E_b, E_c} = \frac{E_b}{2} - \frac{E_c}{2} \tag{2.123}$$

Estado 2: en donde permanece activo durante un tiempo 2.